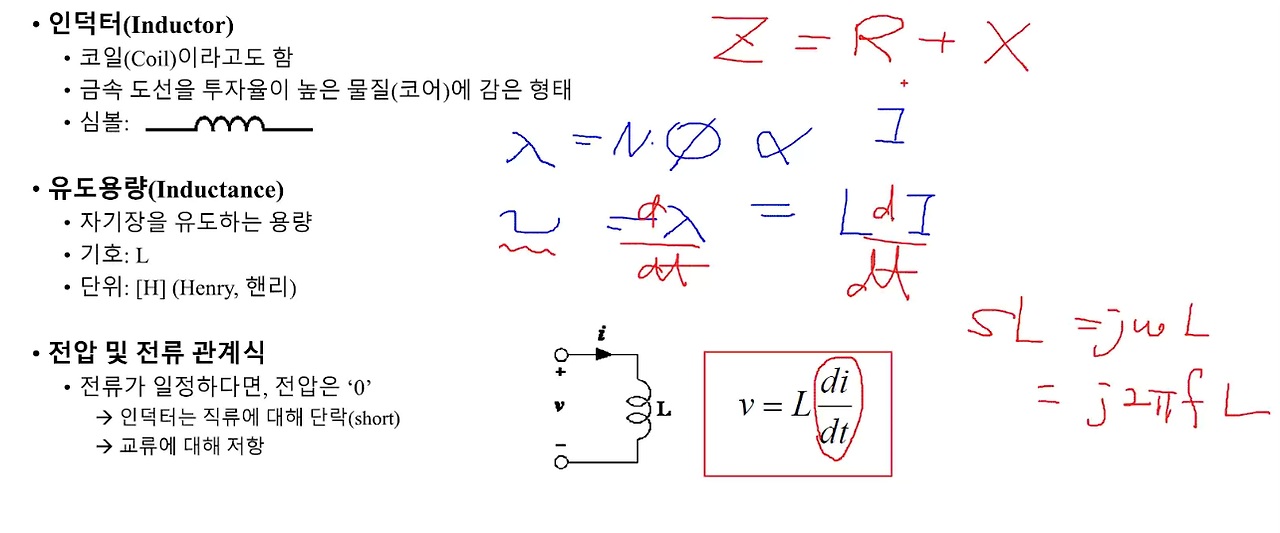

전류가 흐르는곳엔 무조건 L (Inductance) 이 있다. → 기생적인 rlc 값

MOSFET: capacitor 구조 (가운데에 SiO2) 기생적인 c 값

임피던스 : 전압과 전류의 비

위상 변화를 표현하기 위해서 복소수의 형태 사용

중요* 들여다본 저항 구하는법 : open circuit voltage 와 short circuit current의 비

테스트 전원을 달아줘서 구한다.

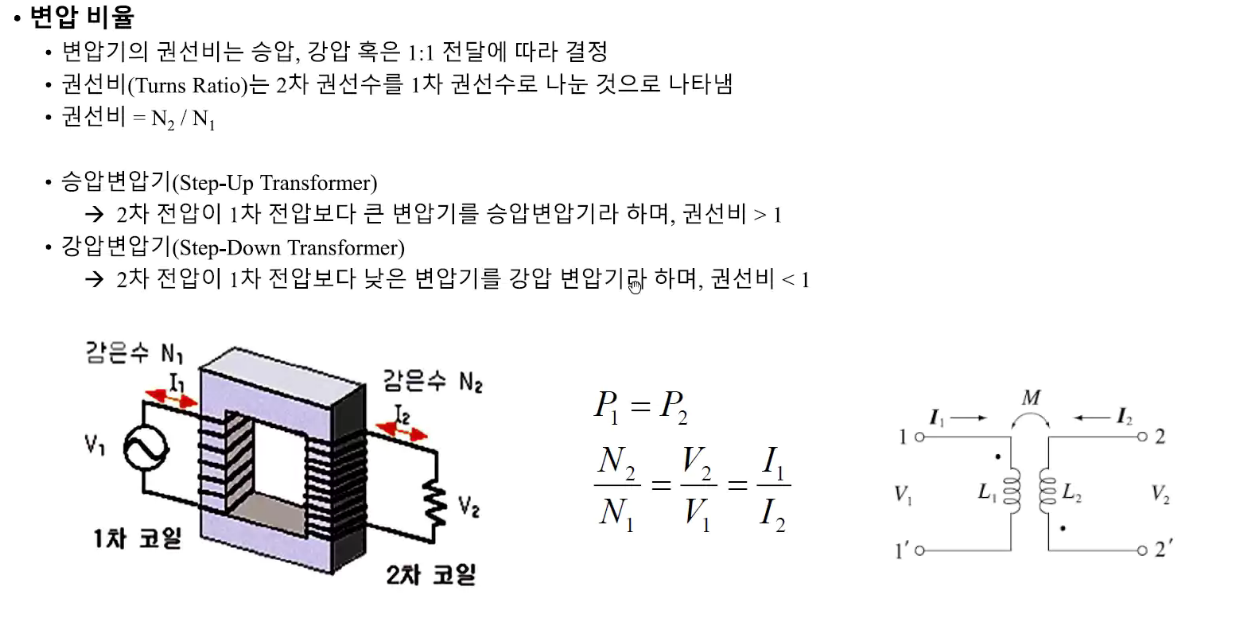

1차측과 2차측은 분리됨 (Isolated). 자속으로 넘어감.

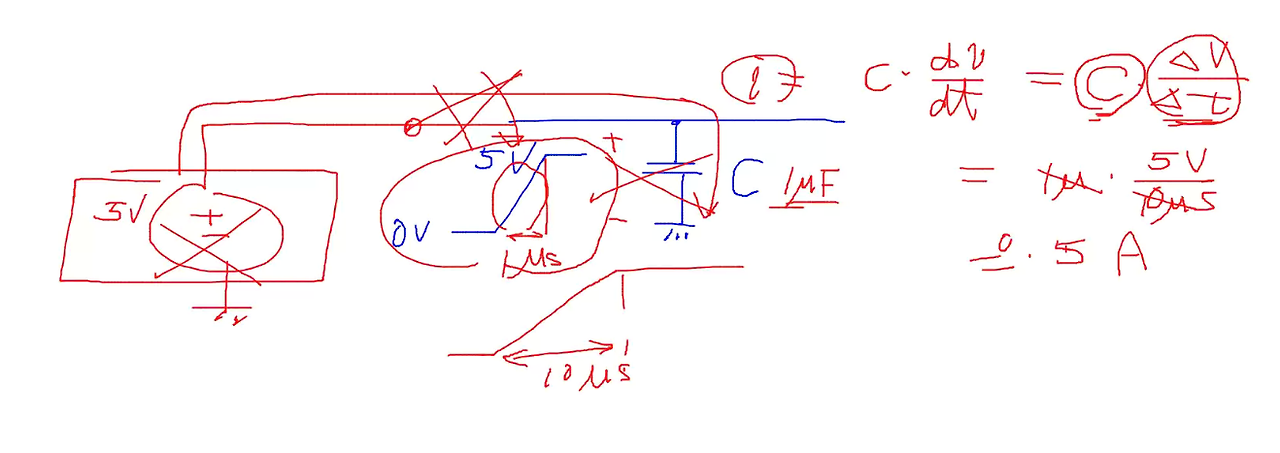

Inrush current: capacitor 전압이 순간적으로 변한다면 큰 전류가 흐를 수 있다.

Inrush current를 줄이는 방법: 전압이 올라가는 시간을 늘린다. 시정수를 사용

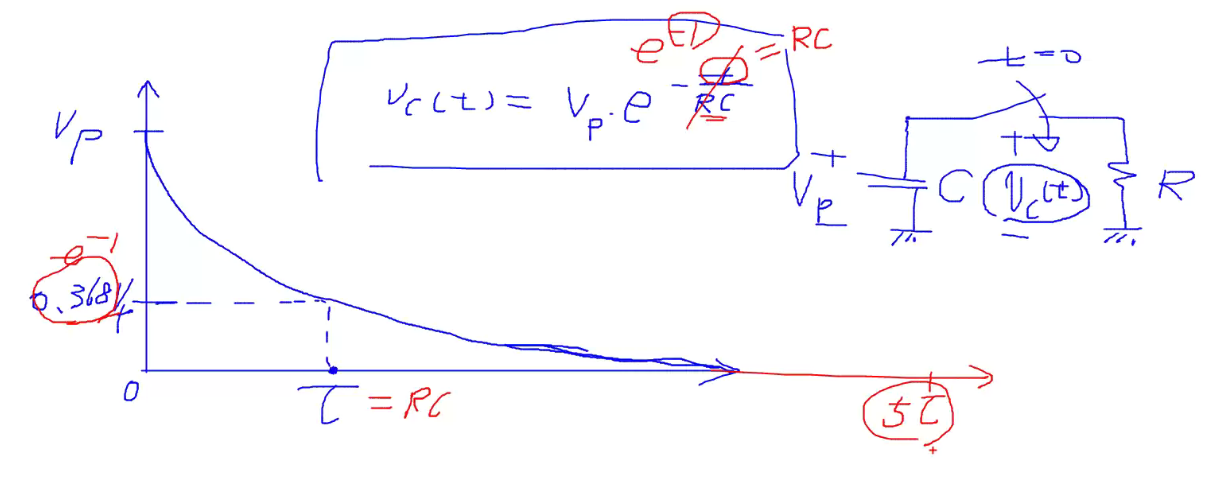

시정수: V_p 만큼 충전되어있는 capacitor가 0.368V_p 만큼 방전될때까지 걸리는 시간

수학적으로 exponential은 0에 수렴하지만 도달하지는 못함. T가 rc라는 시간이 되면 e^-1 = 0.368. e^-5t (<1%)가 되면 완전 방전으로 침.

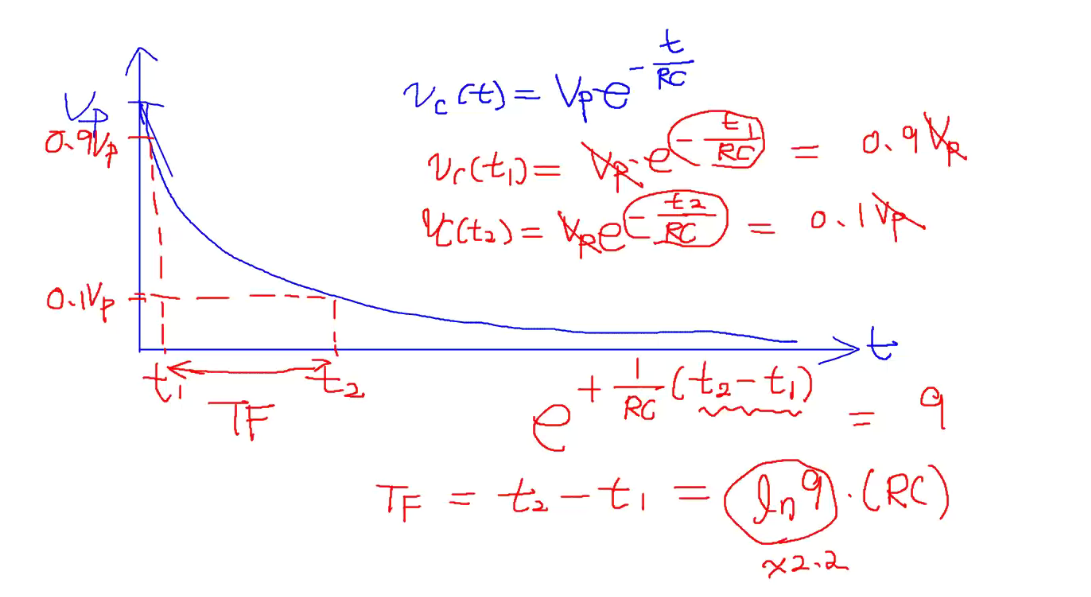

Falling Time 구하기. 위 식을 아래 식으로 나눈다.

시정수의 2.2배 정도 되는 rising/falling time이 생긴다.

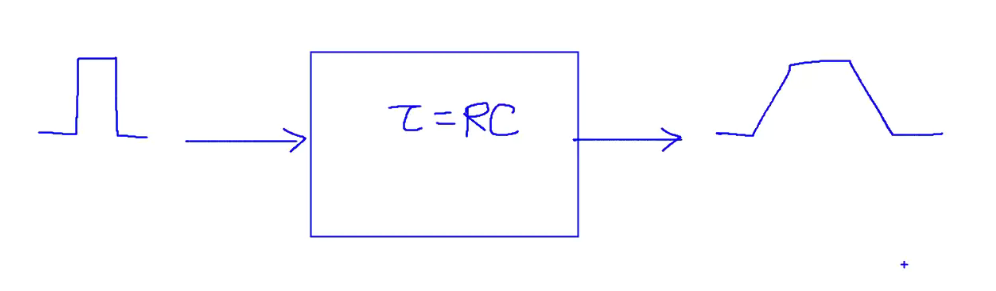

시정수를 적절하게 추가해주면 신호가 늘어지면서 dv/dt가 줄어들어 inrush current가 감소.

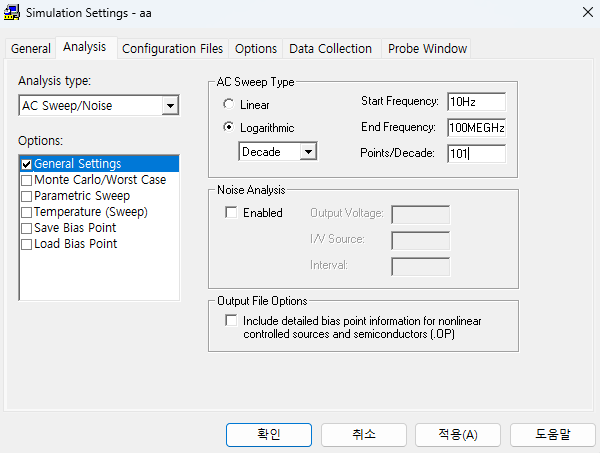

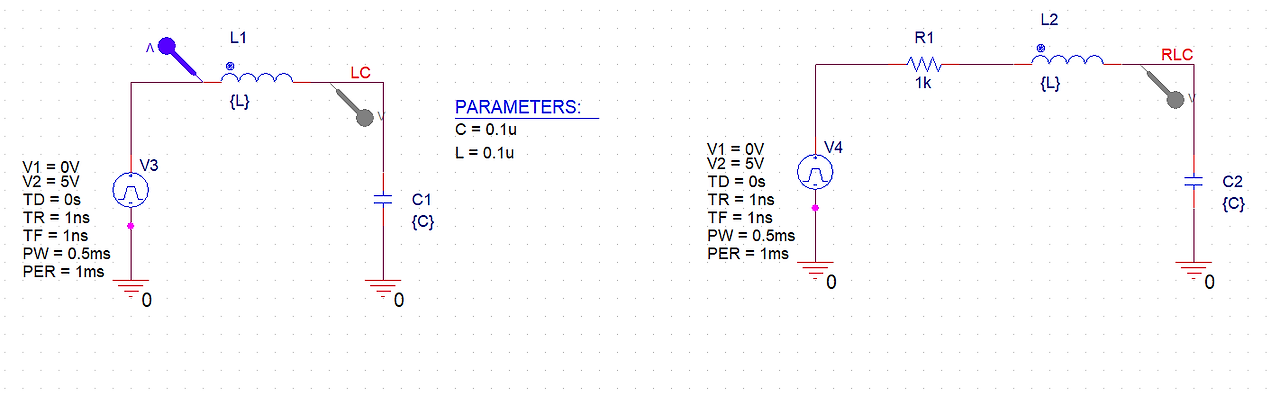

Parametric sweep

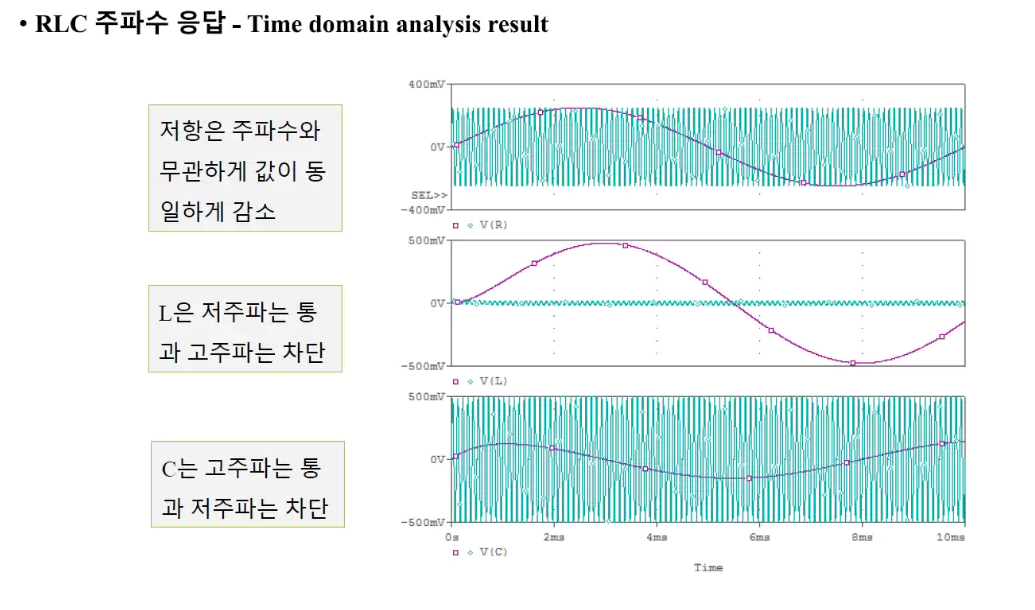

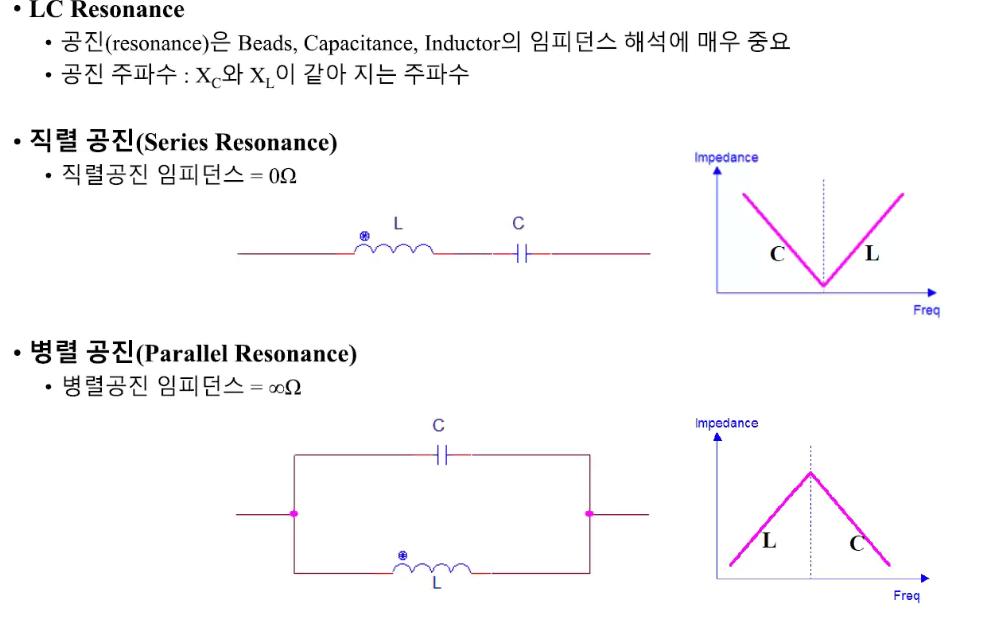

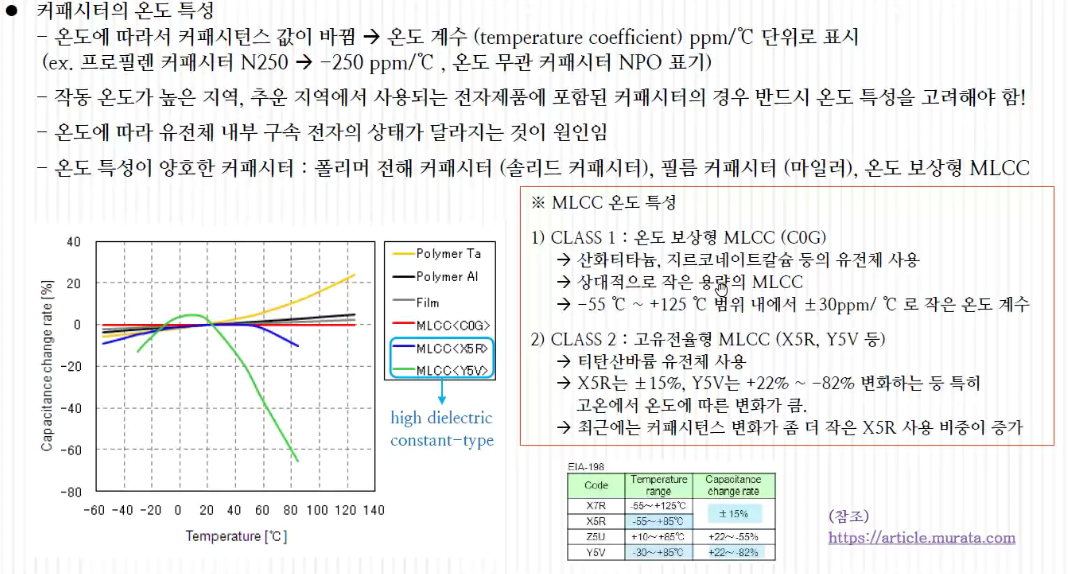

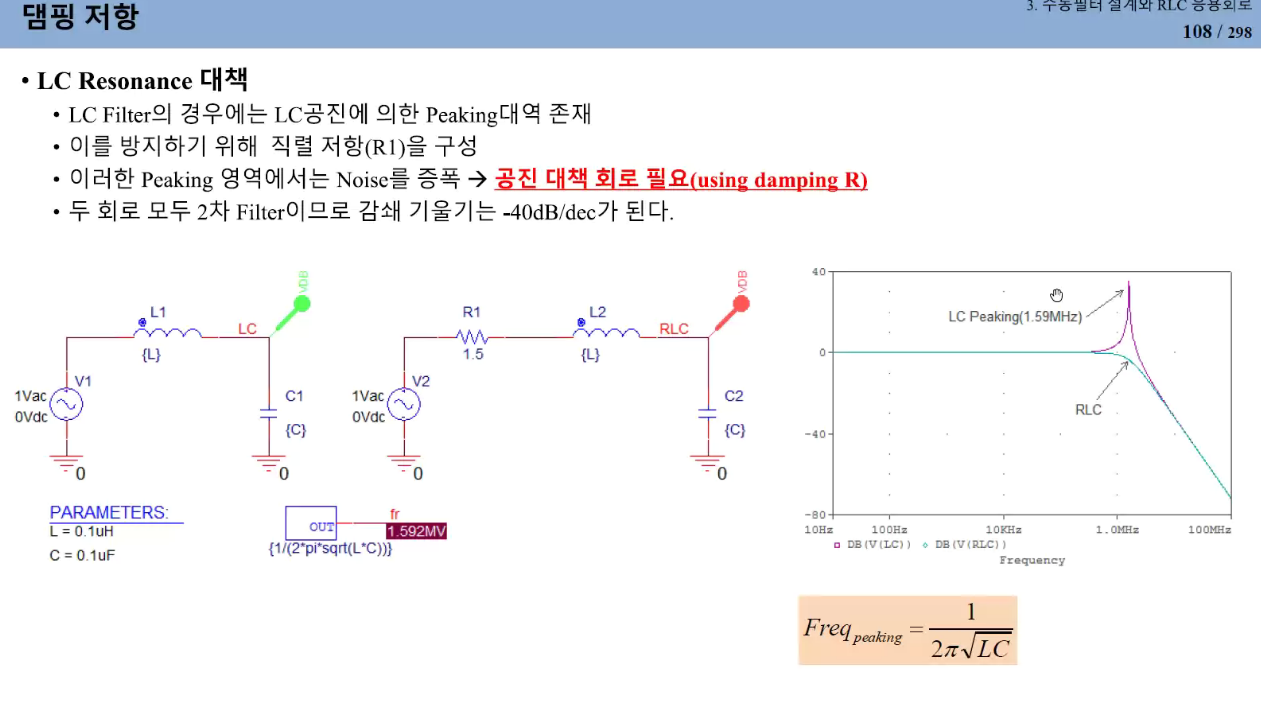

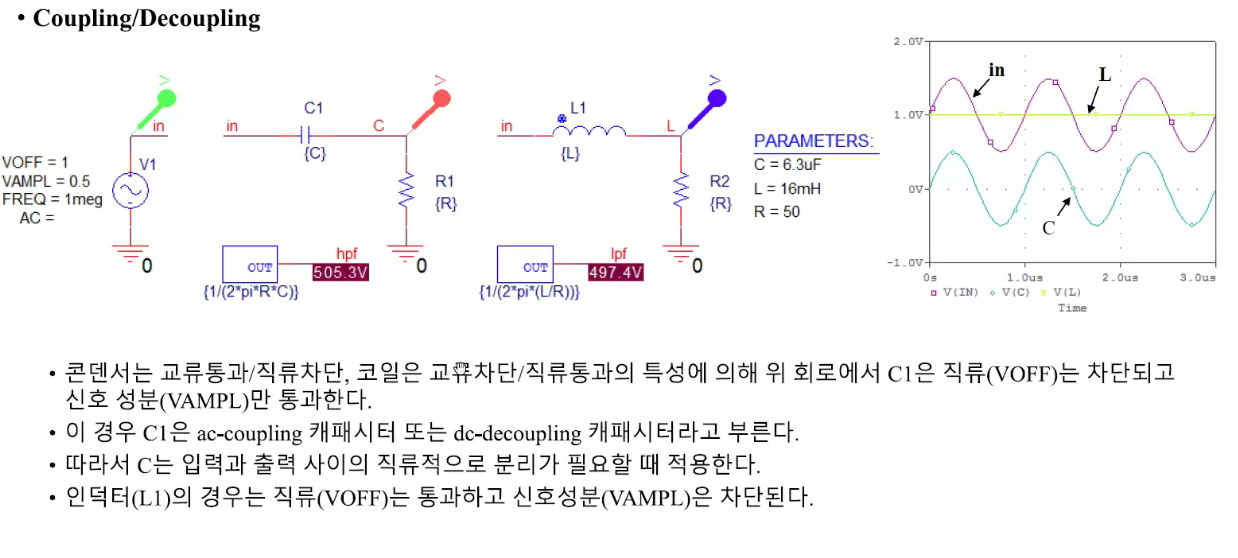

Lc 직렬이 short되거나 병렬이 open 되는 현상. impedance 가 가장 낮을 때 , 높을 때 freq = 공진 주파수 (resonance frequency). 주파수가 높아질수록 capacitor가 RLC의 특징을 가짐.

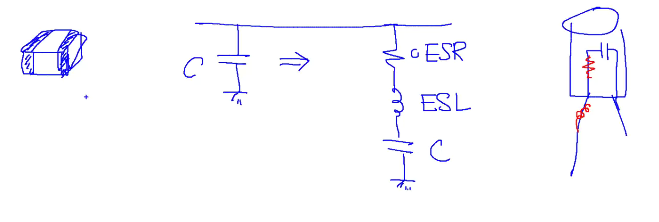

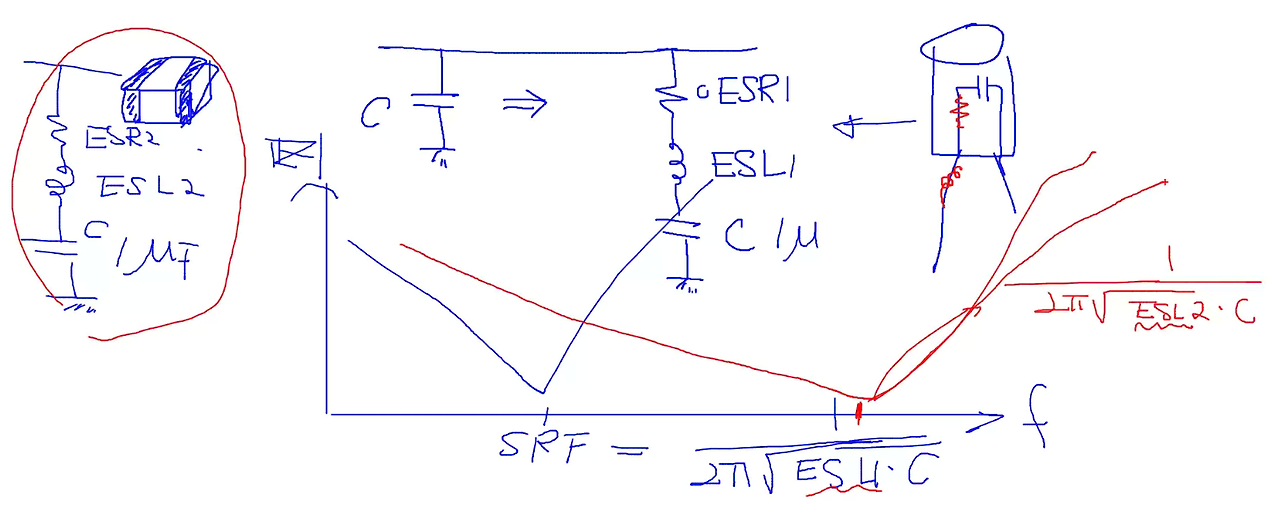

ESR (Equivalent Series Resistance), ESL (Equivalent Series Inductance) ⇒ 기생적인 값

좋은 capacitor (ideal capacitor) 에서는 ESR, ESL이 없음 → ESL, ESR 작을수록 좋음

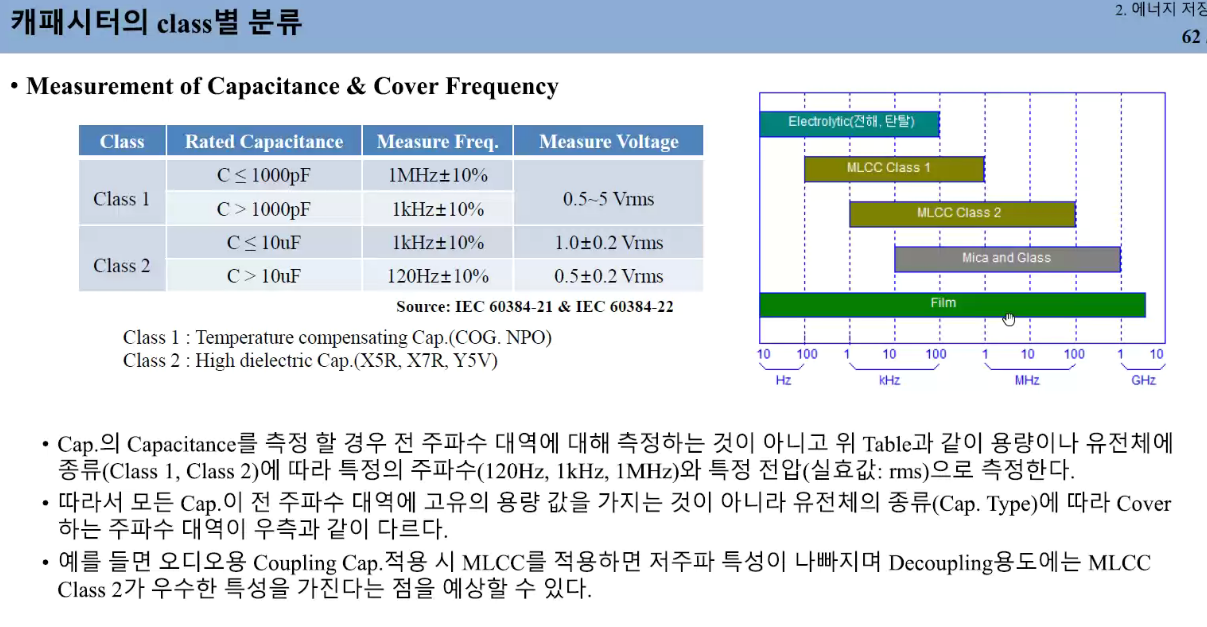

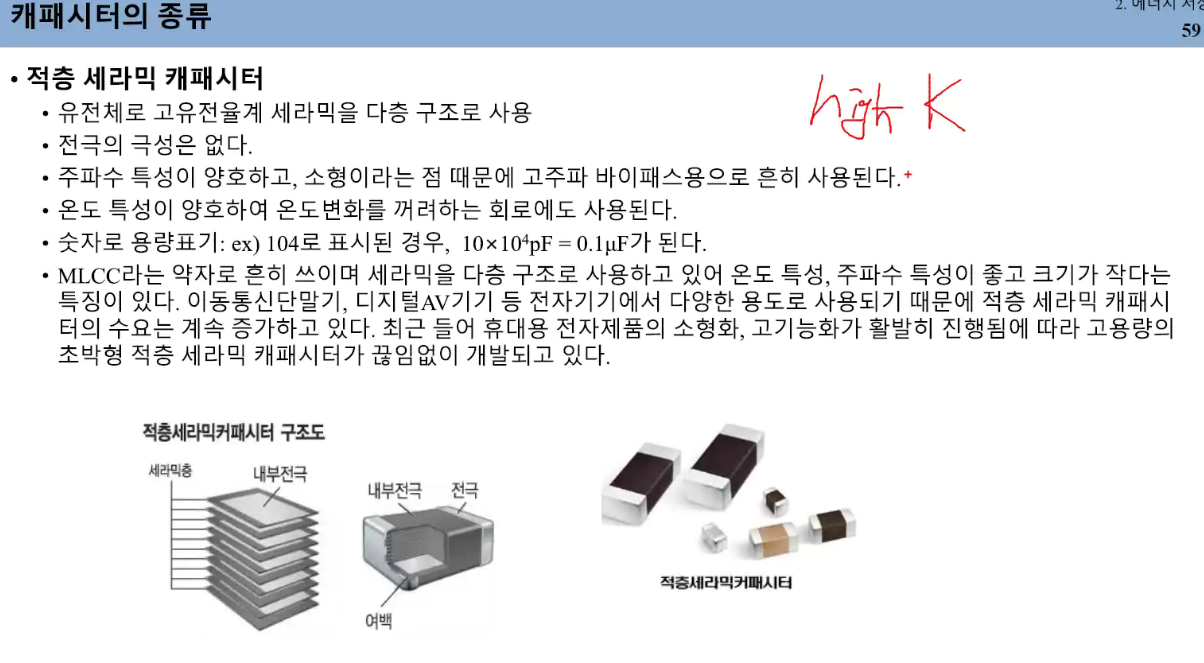

전해 capacitor와 MLCC (Multilayer Ceramic Capacitor)중 MLCC의 ESL과 ESR이 더 작음 (구조상). ⇒ 고주파 특성이 MLCC가 더 좋음.

SRF (Series Resonance Frequency) 왼쪽 : capacitor의 특성, SRF오른쪽 : inductor의 특성 ⇒ capacitor의 정상 범위는 SRF까지.

High K - 유전률이 크다

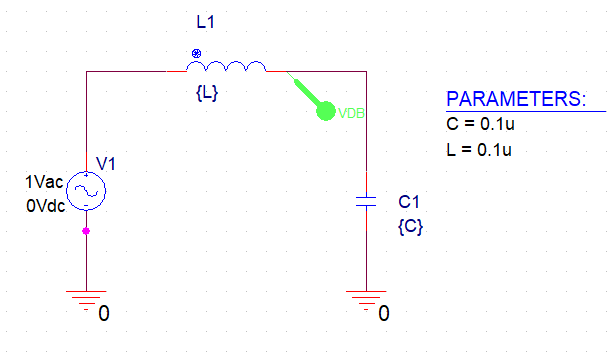

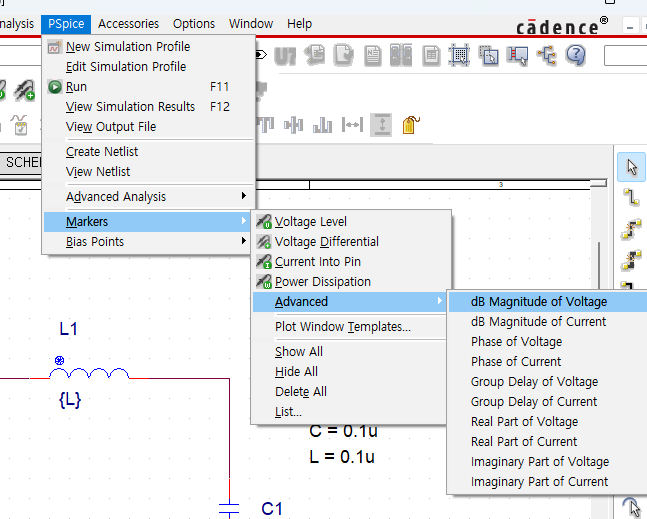

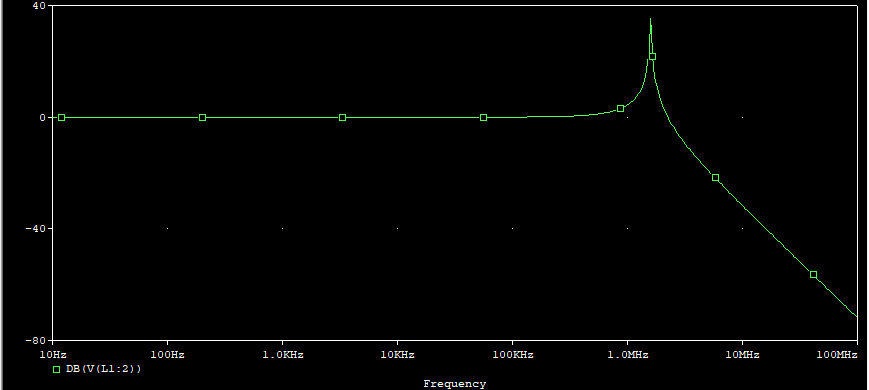

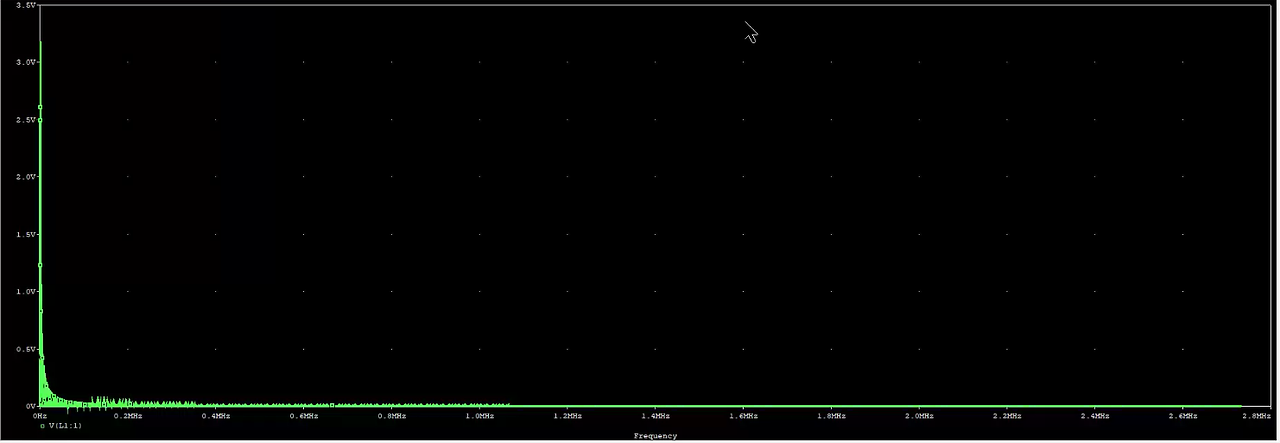

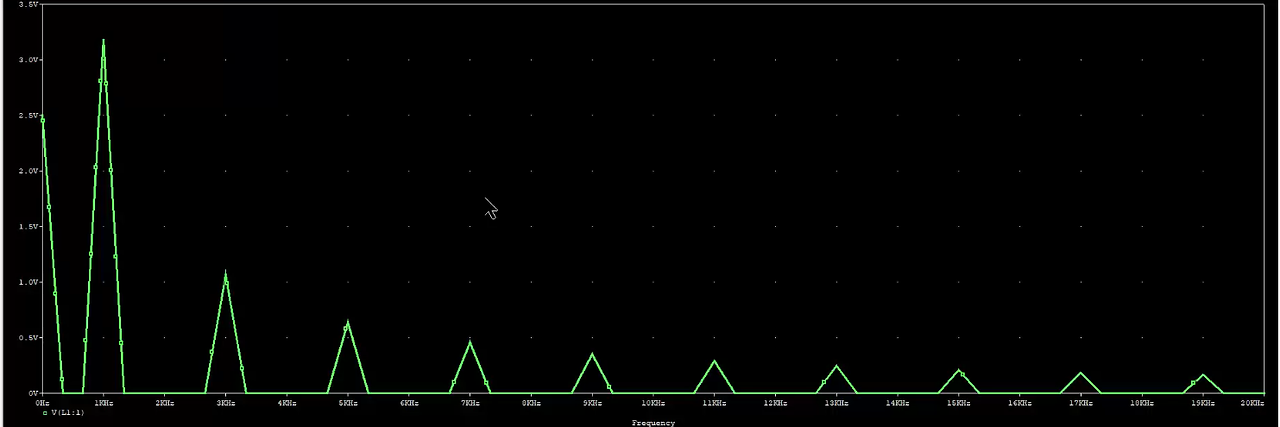

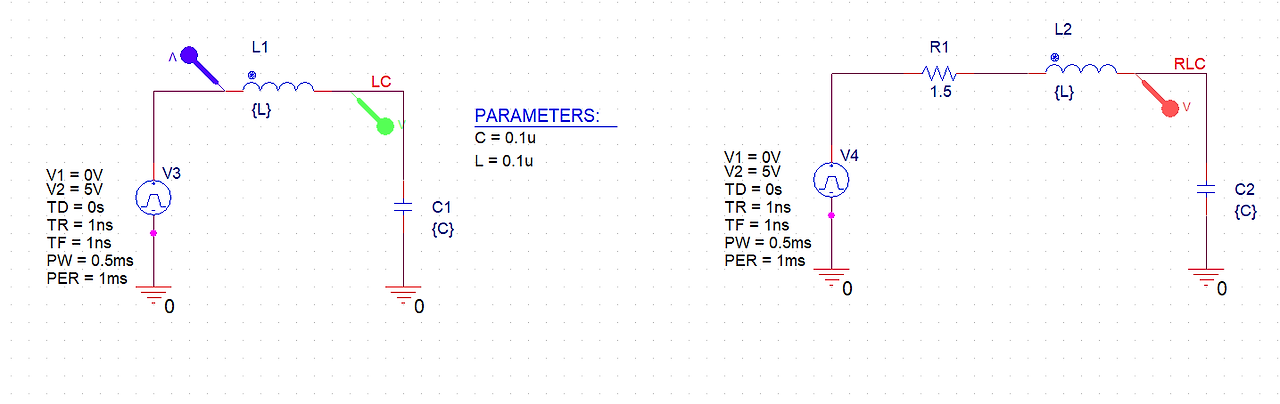

LC 회로 시뮬레이션

0db: 입력이 1일때 출력이 1

공진때문에 peak가 생김 → 공진 대책 회로 필요 (using damping R)

2차 low-pass filter

FFT 적용

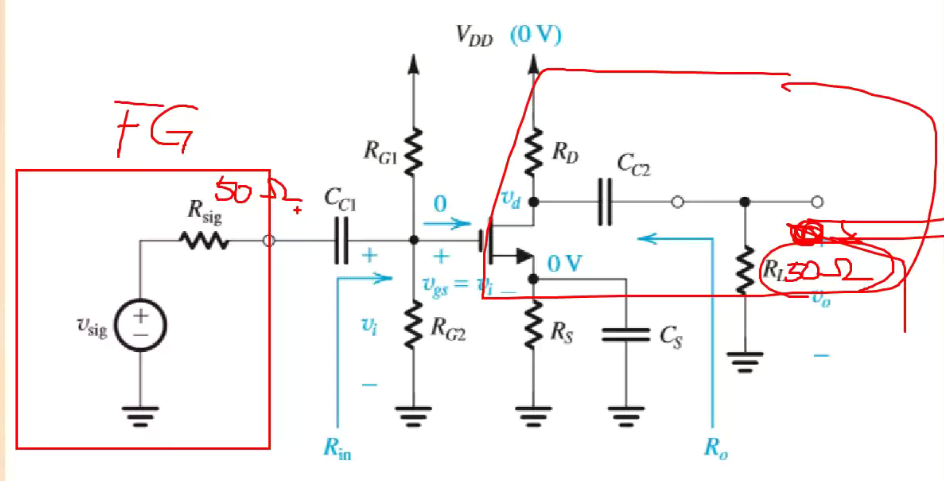

단일 트랜지스터로 이루어진 증폭기 회로 (Common Source 증폭기)

- 결합 capacitor (coupling capacitor)가 달려있음

Function generator

삼각파형 → Sine 파형

Capacitor를 충전 방전 → 미분 하면 pulse 파형 생김 → 다이오드를 사용해 성형해서 sine wave generate

V_sig, R_sig : Function generator

R_l : 부하저항 (load resistor)

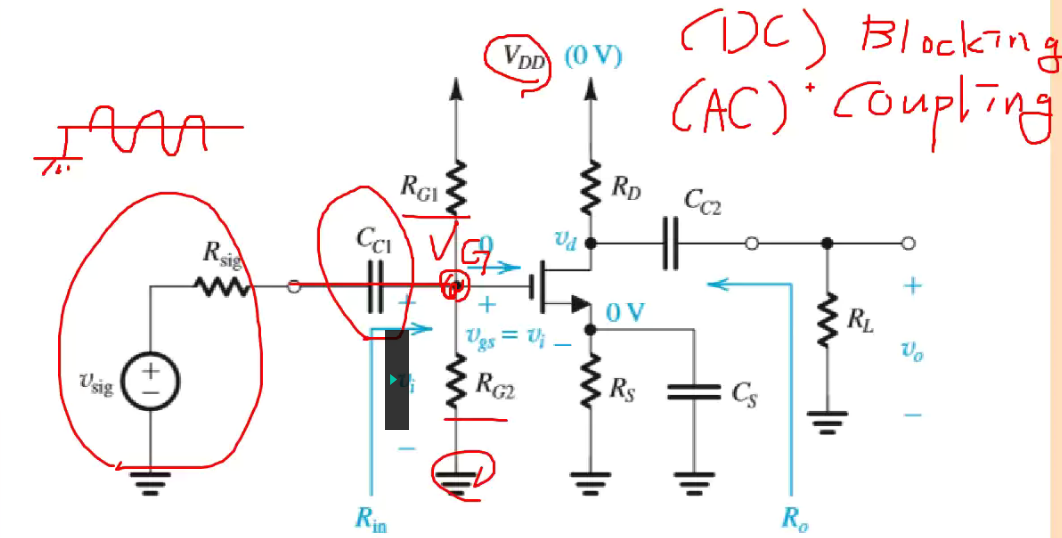

Capacitor 양단자의 DC 레벨이달라도 무시하고 신호만 넘기는 역할 (DC 분리)

높은 주파수 성분들(신호)은 capacitor를 지나간다. → 결합 capacitor (AC coupling capacitor)

DC하고 AC중에서 AC만 통과시킨다.

C_s 는 noise를 빼는 cap이 아니고 신호를 빼는 cap.

Inductor는 DC를 coupling하고 AC를 blocking한다. (실제회로에서는 일반적으로 잘 안씀)

'회로 공부' 카테고리의 다른 글

| Transistor - BJT 응용회로 (0) | 2024.11.11 |

|---|---|

| Diode 응용회로 (2) (0) | 2024.11.11 |

| 전자회로 해석 및 설계 - RLC (마무리), Diode 응용회로(1) (1) | 2024.10.28 |

| 전자회로 해석 및 설계 - RLC (2) (1) | 2024.10.28 |

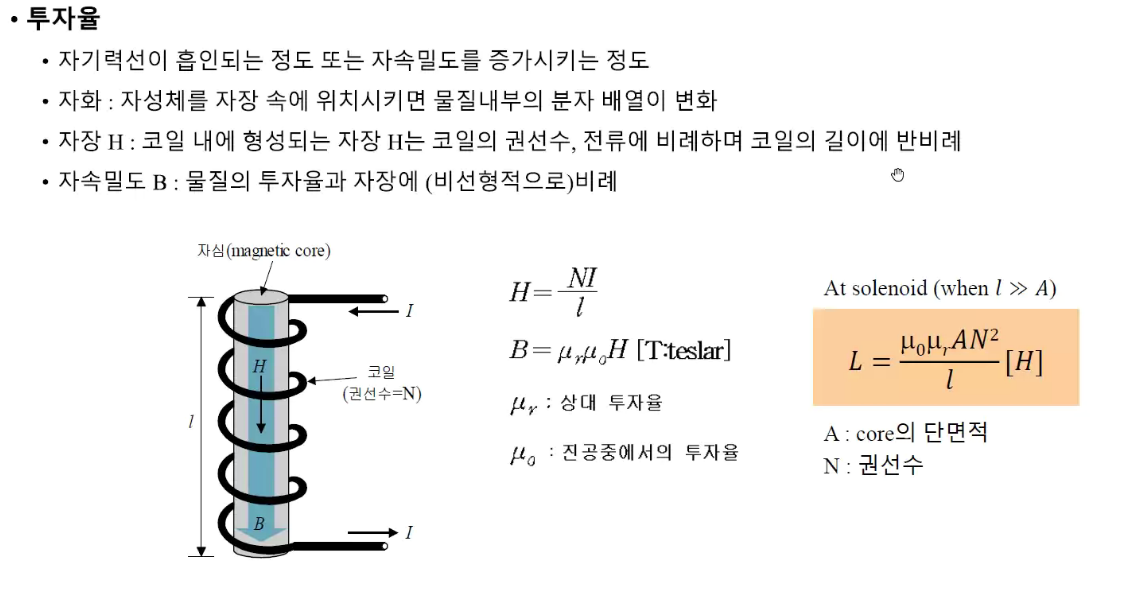

| 전자회로 해석 및 설계 - Inductance, 공진회로 (0) | 2024.10.16 |