지난 내용 복습

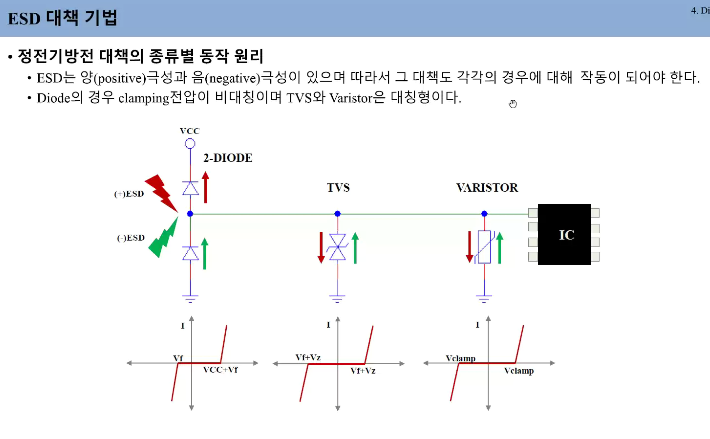

- TVS / varistor에서 클램핑 (전압이 커지려고 하면 쇼트)으로 70% ESD 막아냄.

- TVS 내부 기생 capacitance가 작고 클램핑 전압이 낮아서 varistor보다 더 많이 사용

- IC 자체에서 20% 정도 막아낼 수 있는 능력: 아이오패드라는 부분에서 담당.

- Pcb layout에서 10% 정도 막아낼 수 있다.

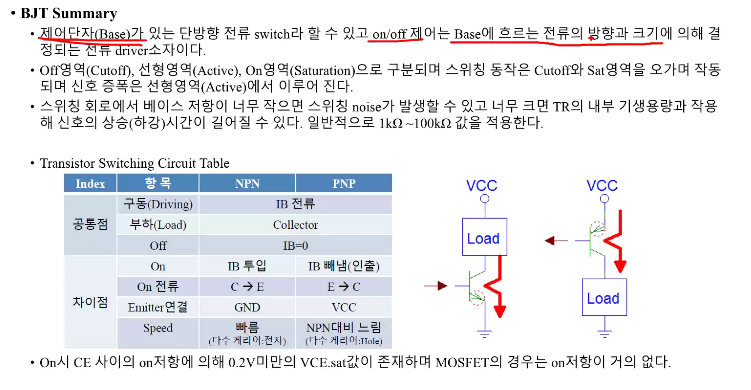

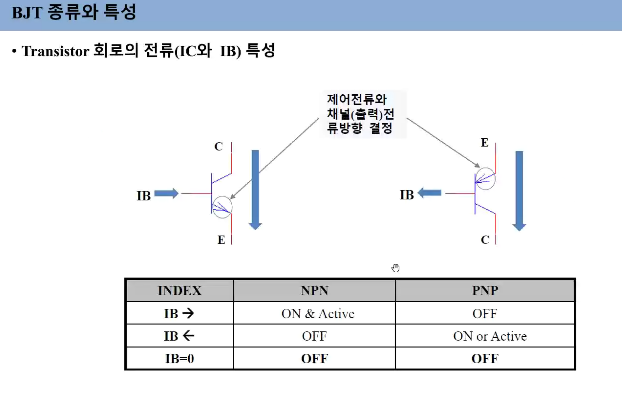

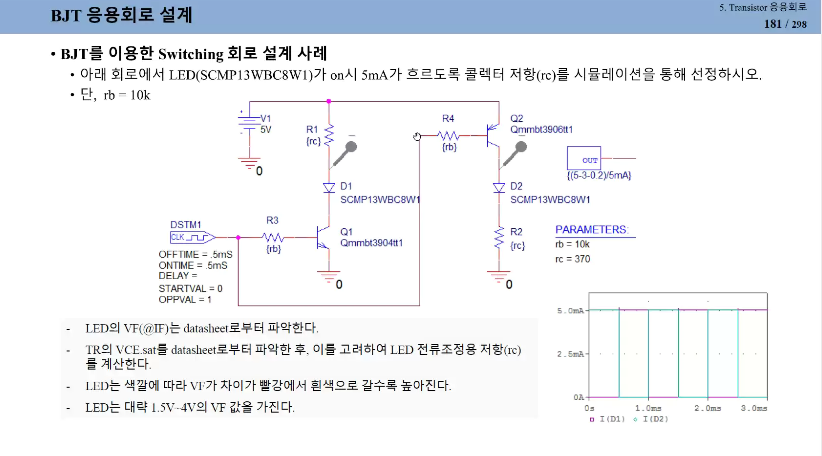

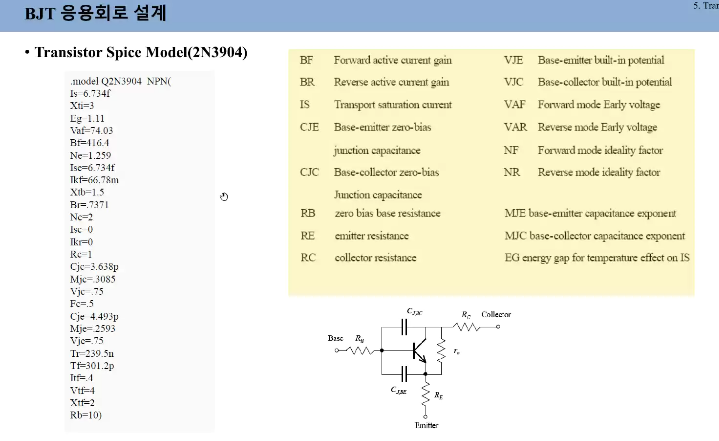

- IC 설계할때 대부분 transistor 사용

Npn이 switch on 되기위한 조건

- Emitter 단자가 ground에 연결

- V_BE (Base에서 Emitter) 0.7v 이상

- 대부분 Collector 단자에 부하 V_cc 연결

Switch 사이에 0.2v 정도 전압차에 의한 power 소모. 스위치가 load보다 아래 달려있음. Low-side switch (NPN, NMOS)

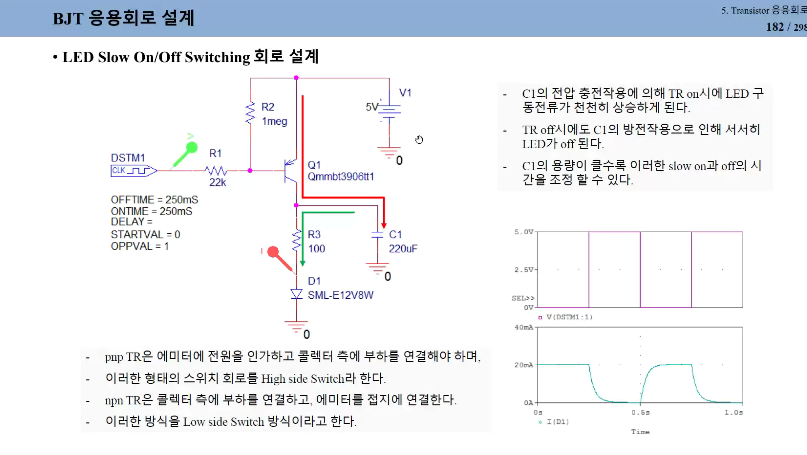

Pnp

- Emitter 단자가 가장 높은 전압에 연결

- Emitter가 Base보다 0.7v 이상 전압이 높으면

- Emitter에서 collector쪽으로 전류가 흐름

- 0.2v 를 VCE(on) 또는 VCE(sat) 이라고 부름

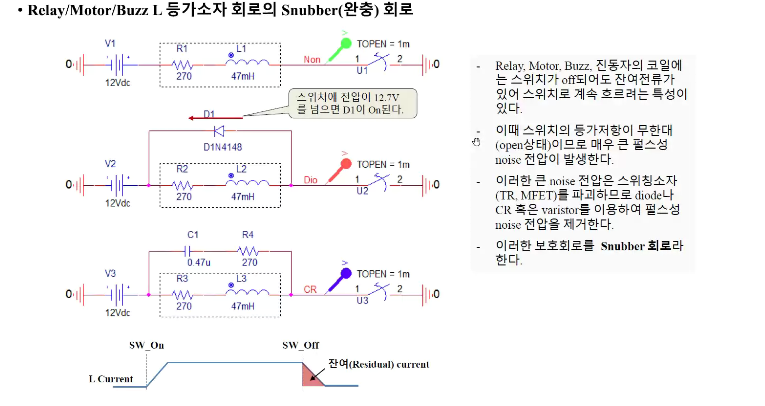

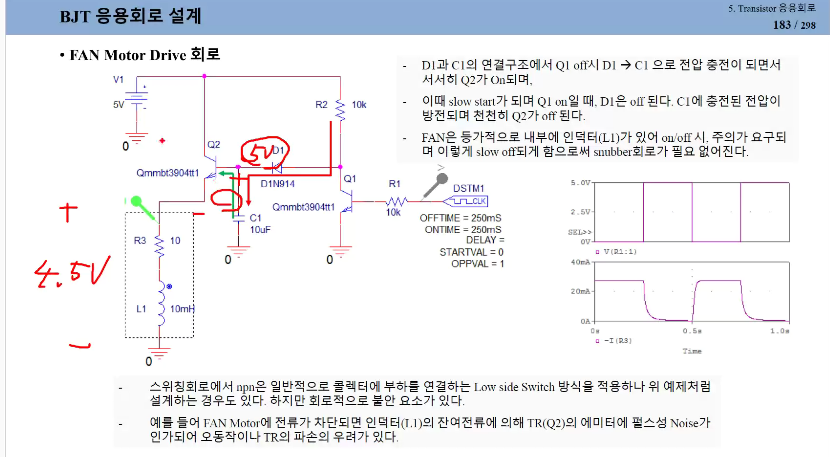

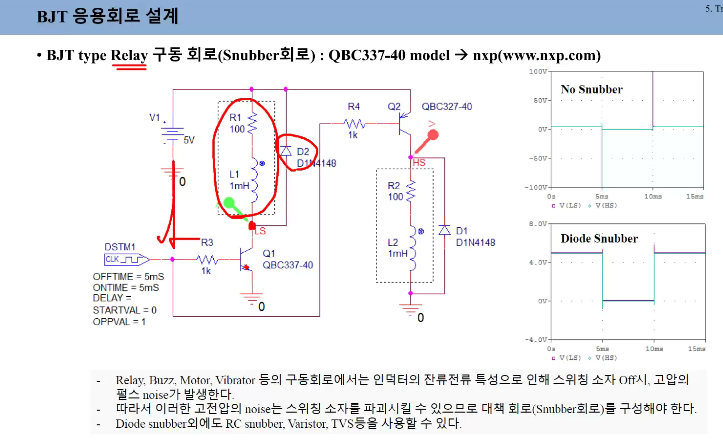

- 인덕터의 전류특성때문에 스위치의 전압이 튀는 현상인데 snubber가 안달려있는 이유?

- Capacitor에 충전 돼 있는 전압을 방전시키면서 동작

- Emitter 단자에 부하를 다는것도 가능하다. 부하에 전압이 크게 걸리면 전압 확보가 어려울 수 있음 주의 할점: 0.7V 확보될수 있도록 주의.

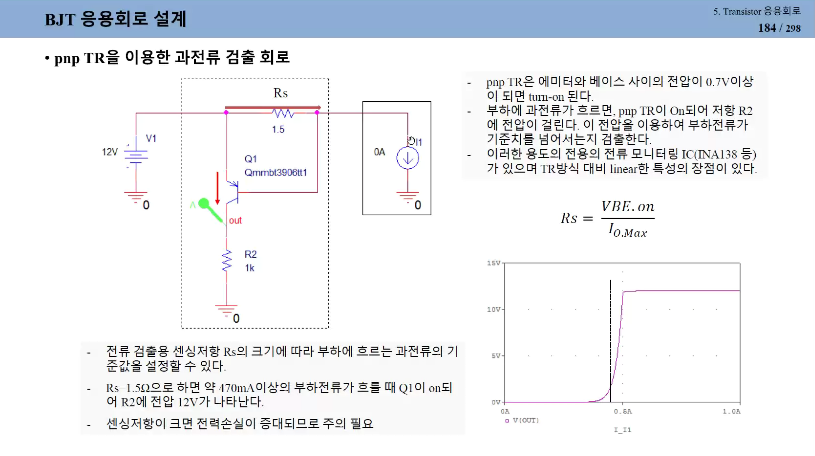

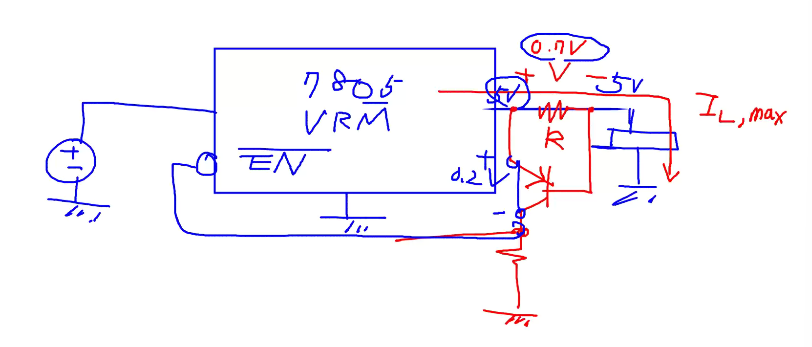

새로운 내용 - 과전류 검출회로

- 원래 흘러야되는 전류보다 더 흐르는 경우 어떻게 검출 할 것인가?

- Voltage regulator는 power를 내기위해 부하쪽으로 전압과 전류를 공급해야된다.

- 부하가 Open 일때 5V 0A. 부하가 short일때 전압이 5V를 내기 위해 무한대 전류를 흘려줘야한다. 실제로는 감당할 수 있는 전류보다 훨씬 큰 전류가 흐를 수 있음. IC가 망가짐.

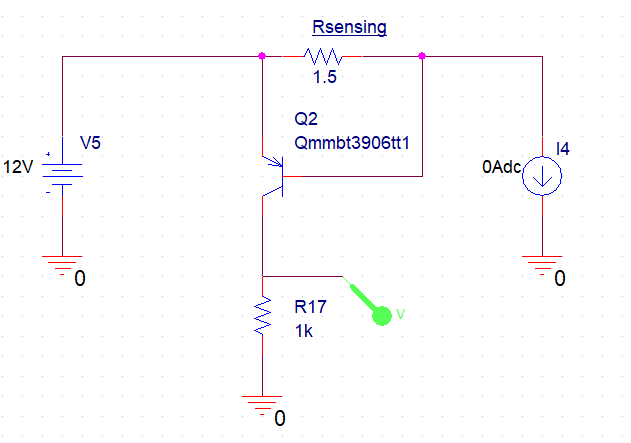

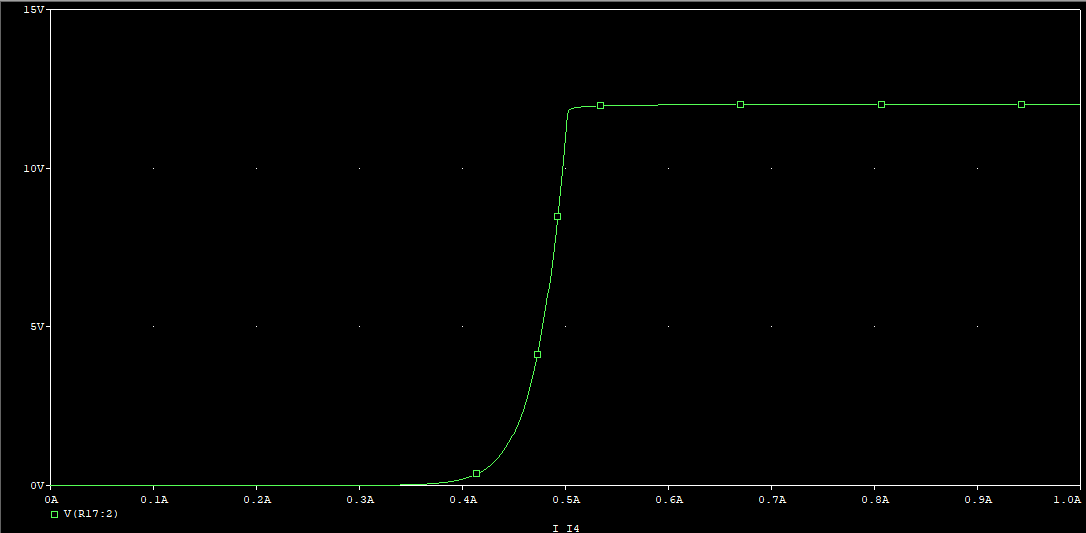

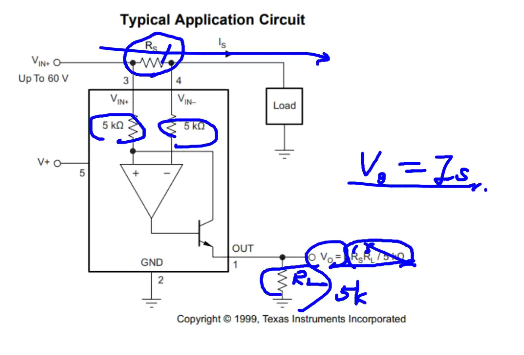

- 전류를 전압으로 바꿔 과전류를 감지. 옴의 법칙을 사용. 직렬 저항을 달아서 저항 양단에 뜨는 전압을 이용. pnp 트랜지스터를 달아서 emitter와 base 사이가 0.7v를 넘어가면 pnp 스위치가 on 되는것을 이용. 허용 가능한 max 전류에 R값과 전류를 곱해 0.7이 되게한다.

- 정상적인 전류가 흐르는 상황에서 0v. 과전류가 흐르는 상황이 만들어지면 4.8v 이상이 뜨게 됨.

- Enable 단자에 연결해서 과전류가 흐르면 IC 동작을 멈추게 할 수 있음.

- Current를 모니터링 하는 circuit

- Snubber가 없을때는 전압이 튀는데 diode snubber를 사용하면 안정된 값이 나온다.

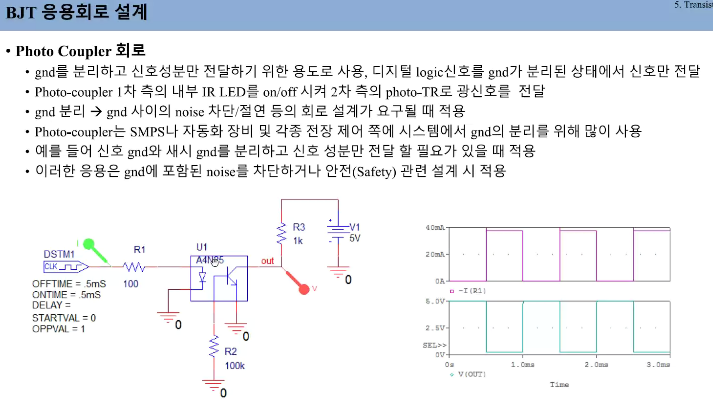

Photocoupler

- 전압이 점점 커지는 아날로그 신호가 들어가면 전압이 점점 커지고 phototransistor도 점점 on 됨. 아날로그 신호도 넘겨줄 수 있다.

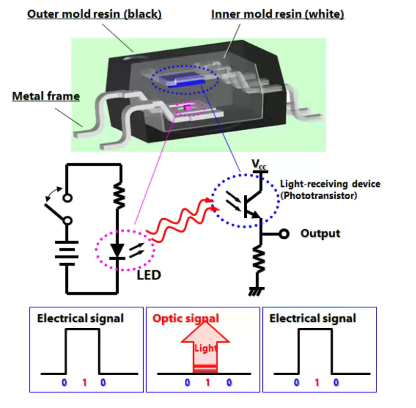

- 신호가 빛의 형태. 신호를 받는 부분은 phototransistor. 빛을 받으면 on, 안받으면 off

- 송신부에서 수신부로 넘기는 신호가 빛. 절연된 상태로 신호를 넘긴다. 이점: 넘겨주는쪽과 받는쪽의 접지가 달라도 됨. 받는쪽이 보내는쪽의 noise의 영향을 안받을 수 있음.

- 절연된 상태로 신호를 보내면 신호를 받을때도 절연된 상태로 받아야한다.

- 내부기생성분

- Capacitance 성분이 switching 회로에 영향을 미친다.