MOSFET

Metal Oxide Semiconductor Field Effect Transistor - MOSFET

- 실리콘 웨이퍼, sub : 기판

- N type을 만드는 과정: diffusion

- 절연체를 올림. SiO2 (이산화규소)

- 절연체 위, n type 위에 Metal 전극을 만들어 놓음.

- 농도가 더 높은 p-type위에도 전극을 단다. 단자 4개.

- SiO2 전극으로 사용하는 물질: polysilicon

- N-type에 있는 전자들을 오른쪽 n-type으로 옮김. 전류의 방향 오른쪽에서 왼쪽.

- 전자들이 왼쪽에서 오른쪽으로 지나갈수 있는 통로 channel을 연결해야 전자들이 안전하게 이동. 만드는 법: 절연체 위에 + 전압을 걸어줌. 왼쪽, 오른쪽에있던 n-type과 아래쪽 p-type에서 전자들이 끌려가서 전자들이 모임. V_t: 문턱전압 (Threshold 전압) 보다 큰 전압을 걸어줌.

- 오른쪽 n-type 에 전압을 걸어주고 왼쪽 n-type에 gnd 연결. 전압차에 의해 발생한 전장에 의해 전자들이 왼쪽에서 오른쪽으로 흐른다. (전장효과 - field effect)

- Diode/ BJT 는 확산에 의한 전류가 흐른다 (diffusion current) - exponential 형태

- MOSFET는 전압차에 의한 전류가 흐른다 (drift (유동) current)

- Mu_n: 전자의 이동도, C_ox: 절연체쪽에서 나오는 C 값

- 가운데: gate 단자 왼쪽: source 단자, 오른쪽: drain 단자

- Souce 와 Gate 사이 전압 V_gs, drain과 source 사이 전압 V_ds

- Source 단자와 body 단자가 묶여있다. IC에서는 연결되어있지 않을 수도 있음. 연결되어있지 않다면 (body단자의 전압이 source단자의 전압보다 0.7v 정도 높으면) pn 접합에 순방향 도통이 되지 않아야한다. Channel에만 전류가 흘러야하므로. Body 전압이 무조건 source와 같거나 다르다면 source 보다 낮아야한다 (역방향 bias).

- NMOS에서 전압이 가장 낮은 전압 : Body

- Body와 Source 전압에 역방향 bias전압이 커질수록 문턱 전압이 커져야한다. → Body effect

- PMOS 에서는 Mu_p : 전공의 이동도. Mu_n이 Mu_p 보다 2~3배 빠르다. LW 값이 커져야지 NMOS와 비슷한 전류가 흐른다.

- 위에 +, 가운데 막혀있고 아래쪽에 - : capacitor 구조. C값이 여러군데에서 나온다. Oxide에서 가장많이 나옴. Oxide에 존재하는 단위면적당 C (C_ox)* 면적 = C. 판과 판 사이의 거리: SiO2의 두께 (tox). Epsilon_0는 진공상태의 유전률 (상수값), Epsilon_r 는 ~3.9. 두께만 알고있으면 C_ox 값 구할 수 있음.

- IC 설계의 디자인 변수: 채널의 길이 L (channel length)를 보면 얼마만큼 미세한 공정인지 판단 가능 (몇 나노 공정). 작을수록 같은 면적의 chip안에 더 많은 transistor → 더 높은 성능. W는 width 채널 폭.

- 10~20% 마진을 주고 gate 단자쪽과 drain단자쪽을 겹치게 만든다 (overlap).

- C_ox*W*L = oxide 전체에서 나오는 C 값.

- C_ov = overlap 되는 부분에 의해서 생기는 기생적인 C 값

- Gate/source 와 gate/drain 사이에 c가 존재한다. (스위치)

- 증폭기로 사용할때는 32개의 기생 c값을 생성한다.

NMOS

- NMOS: N-channel MOSFET

- 처음에는 channel이 없는데 gate와 source사이에 V_gs가 걸리면 channel이 생김 (증가형) : IC에선 무조건 증가형

- 처음부터 channel이 만들어져 있는데 전압을 걸어주면 channel이 없어짐 (공핍형) : 거의 안씀

- 점선이면 증가형, 실선이면 공핍형 (Pspice에서)

- NMOS, PMOS symbol 구분은 화살표로 한다 (p에서 n 방향으로 가리킨다)

- 화살표의 의미: 전류 방향, p→n 방향

- Body → 기판 : NMOS

- 기생적인 diode성분. 도통되지 않도록 body단자의 전압을 같거나 역방향으로. Switch에서는 source와 body가 붙어있어 왼쪽 diode성분은 무시가능. 오른쪽 diode 성분은 중요. 없으면 안되는 스위치도 있음 (양방향 스위치). 스마트폰의 충전 단자에서 전류가 들어오거나 나갈 수 있어야함. Body와 drain 단자 사이의 다이오드를 symbol에서 그려줌.

어떻게 하면 NMOS를 on/off 시켜서 switch로 쓰기 위한 조건

- Source 전압이 가장 낮아야함 (GND에 연결)

- Gate와 source사이 전압이 문턱전압보다 커야한다. (Channel을 통해서 Drain에서 source로 전류가 흐름, load가 drain에 달려있음) , load는 drain단자쪽에 달림.

- MOSFET는 on 됐을때 양단에 걸리는 전압이 거의 없다 (작다) → power 소모 적음 → 모바일 기기에 사용가능

- 모든 NMOS의 바디는 공통

PMOS

- Body에 해당하는 n-type 우물 n-well을 만든다.

- 전공으로 이루어진 channel을 만드려면 Source 단자에 Gate단자보다 높은 전압.

- Drain단자에 source 보다 더 낮은 전압

- 가장 높은 전압 : source. 가장 낮은 전압 : Drain

- 전류가 source에서 drain쪽으로 흐른다.

- NMOS, PMOS 동시에 만든것 : CMOS

- NMOS와 PMOS의 차이점: 모든 NMOS는 Body부분이 묶여있음. PMOS들은 바디가 다른 well에 따라 분리될 수 있음. Body 전압이 가장 높은곳에 연결되어야한다. Body effect가 안생긴다.

- NMOS 입력단을 쓰는 차등증폭기 : body effect가 생김, PMOS : well을 따로 쓰면 body effect가 없다.

- P-type channel에서 n-type 바디 쪽으로 화살표 (symbol)

- Drain에서 source방향으로 diode.

NMOS를 switch로 사용하기 위한 조건

- 가장 높은 전압 : source. (V_DD연결)

- PMOS의 문턱 전압이 -로 정의되어있다. 기준이 NMOS이기 때문. Source와 gate사이에 걸리는 전압이 문턱전압의 절대값보다 커야함. (크면 on, 작으면 off)

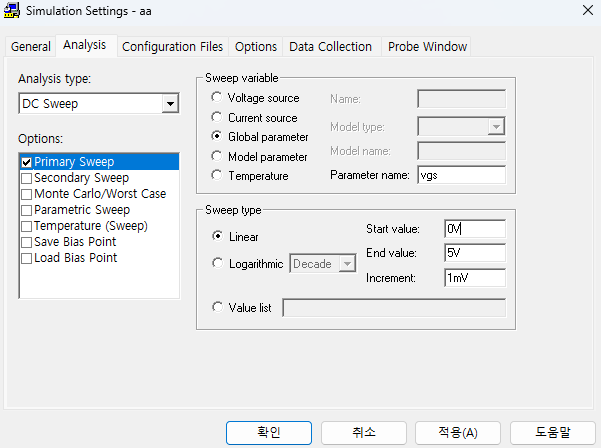

전압원의 값을 변수로 잡는다. X축의 변화를 보면서 언제 switch가 on되는지 보고싶음.

NMOS 문턱전압 2.8V 근처 PMOS 문턱전압 -3.7V 정도

NMOS 문턱전압 V_to = 2.831 임을 확인

PMOS 문턱전압 -3.67확인 .

5V 1k 5mA전류가 흘러야함

- 4.99 전류 흐르는걸 확인. BJT에 비해 파워소모 적음.

2N7002 와 같은 mosfet은 굉장히 급하게 올라가는 기울기 → 증폭기로 사용하지 않는다.

- 입력에 0V → 출력에 5V, 입력에

- Gate와 drain사이 기생 c_gd 때문에 튀는 값 발생

방지 어떻게?

- Bjt에서는 커패시터를 달아줬는데 이미 c_gs가 있어서 저항을 달아 RC시정수 생성

- 더 큰 저항일수록 dv/dt 작아짐 → 10kOhm 에서 100kOhm. 너무 큰값 안됨.

튀는 값 거의 사라짐. 이 상황을 모르면 gate 단자의 무한대저항에 직렬저항을 다는꼴. 이해를 하면 MOSFET를 switch로 사용할때 gate단자에 저항이 필요하다 라는것을 안다.

저항을 다는 또다른 이유: gate단자를 보호하는 역할. Capacitor와 똑같은 구조, 저항이 ESD같은 큰 dv/dt가 들어오는 것을 방지할 수 있음. 흐르는 전류가 저항때문에 줄어듦.

숙제: 저항값이 얼마가 되면 5mA가 흐를까?

1. p184 : 부하 전류가 1 A 일 때 12 V 가 출력되는 과전류 검출회로를 설계하시오.

2. p204 : 5 mA가 흐르도록 LED 스위칭 회로를 설계하시오.

참고할만한 링크

https://news.skhynix.co.kr/post/the-deprived-the-crystal-of-alchemy

'회로 공부' 카테고리의 다른 글

| Switching 응용회로 / Comparator (1) | 2024.11.11 |

|---|---|

| MOSFET Load Switching 회로 (0) | 2024.11.11 |

| Transistor - BJT 응용회로 (0) | 2024.11.11 |

| Diode 응용회로 (2) (0) | 2024.11.11 |

| 전자회로 해석 및 설계 - RLC (마무리), Diode 응용회로(1) (1) | 2024.10.28 |