어제 내용 복습

- PMOS에서 Well을 별도로 만들면 body를 분리시킬 수 있음

- PMOS에서는 gate전압을 source 전압보다 낮게 줌. V_SG > |V_tp| 이면 channel이 만들어진다. Drain 단자가 source보다 낮아야한다.

- NMOS → source 전압 가장 낮음. PMOS → source 전압 가장 높음.

pg 198.

- BJT 에서는 base와 collector전류를 그려봤을때 원만한 구간 → 증폭기로 사용가능

- MOSFET는 V_GS와 전류를 그려봤을때 문턱전압을 지나는 순간 가파르게 상승 → 증폭기로 사용 불가능

- MOSFET는 switch on 됐을 때 source와 drain사이에 전압이 거의 0에 가까워 파워소모 굉장히 작음

- 반도체 소자에 가장 크게 영향을 주는 문턱전압도 온도에 따라 달라진다.

- Pspice 기본온도 설정 섭씨 27도

- 온도 변화를 줬을 때: 온도가 올라갈수록 문턱전압이 감소함.

- MOSFET는 parameter가 매우 많다.

- 가장 중요한 문턱전압 (V_to) 조차도 손으로 계산하기 힘들다. Parameter들이 계속 물려있음. 가장 편하고 많이 사용하는 방법: simulation 돌리기.

- 스위치 용도로 쓰는 mosfet는 level3 정도면 충분히 제역할을 함.

- L이 2um 정도면 long channel. L값이 작아질수록 예상하기 힘든 parameter들이 많음 → 정교한 모델 사용 요구.

- Level 1은 주로 교육용

- Gamma - body effect 관련 parameter

MOSFET에 저항을 달아주는 이유는 여러 가지가 있습니다. 저항을 추가함으로써 회로의 안정성을 높이고, 특정 동작 조건을 제어하며, 전류 흐름을 조절하는 등의 다양한 목적을 달성할 수 있습니다. 주요 이유들을 다음과 같이 정리할 수 있습니다:

1. 게이트 저항 (Gate Resistor)

- 스위칭 속도 조절: 게이트 저항은 MOSFET의 스위칭 속도를 조절할 수 있습니다. 큰 게이트 저항을 사용하면 스위칭 속도가 느려지고, 작은 저항을 사용하면 스위칭 속도가 빨라집니다. 이를 통해 스위칭 노이즈와 EMI (전자기 간섭)를 줄일 수 있습니다.

- 게이트 충전/방전 전류 제한: 게이트는 캐패시터처럼 동작하며, 스위칭 시 게이트 충전/방전 전류가 발생합니다. 게이트 저항을 추가하면 이 전류를 제한하여 드라이버 회로를 보호할 수 있습니다.

2. 드레인 또는 소스 저항 (Drain or Source Resistor)

- 전류 측정 및 피드백: 드레인 또는 소스에 저항을 추가하면 전류를 측정할 수 있습니다. 이 전압 강하는 피드백으로 사용되어 전류 제어 회로를 구성할 수 있습니다.

- 열 분산: 저항을 사용하여 전류를 분산시키고 MOSFET의 발열을 줄일 수 있습니다. 이는 MOSFET의 온도 상승을 억제하여 안정적인 동작을 보장합니다.

- 안정성 향상: 소스 저항은 소스 폴라 전압을 증가시켜 MOSFET의 안정성을 향상시킵니다. 이는 소스 저항 피드백으로 인해 게이트-소스 전압을 일정하게 유지하는 데 도움이 됩니다.

3. Pull-Down 저항 (Pull-Down Resistor)

- 게이트 플로팅 방지: 게이트가 플로팅 상태가 되지 않도록 pull-down 저항을 사용합니다. 이는 MOSFET이 예기치 않게 켜지거나 꺼지는 것을 방지합니다.

- 저항이 달려서 나오는 트랜지스터: 디지털 트랜지스터

- MOSFET는 switch가 on 되는 상황이 channel이 만들어질때 저항성분 으로 표시되어있음 R_DS (on)

- MOSFET는 큰 전류가 흐를때 큰 전압이 뜰 수도있음. 모바일 기기처럼 흐르는 전류가 작을때 상대적으로 작은 power 소모.

- Gate/source (입력신호가 들어가는곳) input capacitance (C_gs = C_iss) , Gate/drain (출력신호가 나가는곳) output capacitance (C_gd = C_oss)

- C_iss 값이 커지면 신호가 적분특성으로 천천히 늘어진다 → on/off switching에 영향을 줌 → 고속 switching이 안됨

- 고속 switching이 되려면 입력단에서 보는 input capacitance C_iss가 작아야함

열저항 - 얼마만큼 열 방출이 잘 되는가

- Junction temperature T_J = T_A (Ambient temp) + P_max*R_theta (열저항)

- 온도를 줄이려면 방열판을 달아서 열저항을 떨어뜨려야함

- V_DS, V_GS : drain/source 사이에 걸릴수 있는 최대전압 60V. Gate/source 사이에 입력이 들어가는데 +/- 30V 가 들어오면 망가진다. +/- 30V 내에서 클램핑을 해줘야함.

- 큰틀에서 봤을 때 BJT와 MOSFET의 동작이 비슷하다.

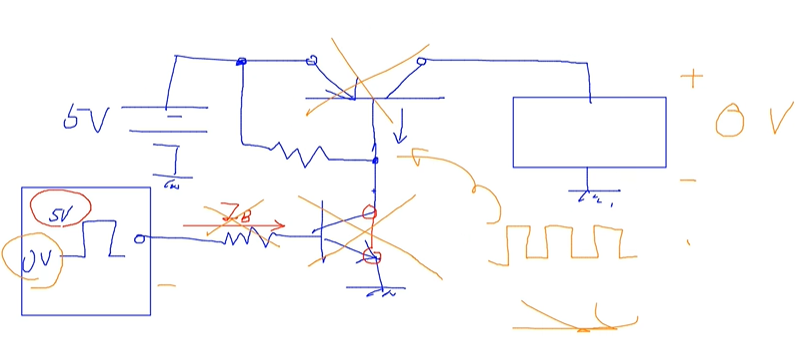

BJT Load Switching

- 부하에 스위치를 달아 on/off

- 스마트폰을 켰을 때 무조건 작동하는 기능- 전화, sms (끌 수 없음)

- Load switch의 역할: dc전압을 뒷단 부하쪽에 넘겨줄지 말지를 결정 (ic의 전원단자에 연결).

- 배터리 전압을 읽어오는 회로 - 배터리 잔량 표시 어떻게 구현? 일정시간 간격으로 읽어옴. 연결했다가 안했다가 (load switch)

- Base 전류가 흐르지 않으면 아래쪽 npn switch가 off되면 전류가 흐르지 않는다. 연쇄적으로 위에 있는 pnp 스위치도 off. 부하에 걸리는 전압 0

- 회로에 floating이 있으면 noise발생 할 수 있음 → 저항을 하나 입력전압에 달아놓음. Pull up 저항.

- 단점: 0.2V 정도의 Vc_sat이 뒷단 ic로 갈때 20mW의 power 소모. 위쪽에 흐르는 전류 : ic를 동작시키기 위한 전류. 아래쪽 전류 : 스위치를 동작시키기 위한 전류. 위쪽에서 power 소모가 커진다.

- 해결 방법: 상대적으로 power소모가 적은 cmos로 바꾼다. 위쪽 PMOS, 아래쪽 NMOS로 바꿔줌

MOSFET Load Switching 회로

- PMOS: source가 가장 높은 전압에 연결

- 위쪽 PMOS의 source와 gate사이에 거의 5V 걸리고 뒷단 ic에 걸리는 전압: 거의 5V

- 0V → 아래쪽 NMOS off → pull-up 저항에 전류가 안흐르고 PMOS off → 전류가 흐르지 않아 IC에 0V.

- 단점: 가격이 비싸다.

혼합형 (Hybrid 타입)

- 엔지니어가 하는일의 대부분: 비슷한 동작을 하는 회로를 가격이 더 싸게 만드는것: 원가 절감 (삼성에서 vale innovation이라고 부름)

- 위쪽 PMOS는 바꿀 수 없음. 아래쪽 NMOS를 npn 트랜지스터로 만들 수 있음.

- 5V를 넣으면 base전류가 npn on 시키고 연쇄적으로 pmos on 시킴. 5V나 4.8V나 위쪽 PMOS의 문턱전압보다는 높음. NMOS를 썼을때보다 약간의 power 소모.

- 아래쪽 npn조차도 안쓸 수 있으면 가장 싸지 않을까?

- 제어전압을 npn없이 다이렉트로 연결. Source 5V, gate 5V → 전압차 0V switch off. Source 0V, gate 5V → switch on → 반대이긴 하지만 동작함.

- 왜 이중으로 쓰느냐?

- 단순형 (스위치 하나만 쓰는것) 의 단점

- 넘겨주는 전압과 제어 입력 전압이 동일할 때는 동작하나 둘이 다를때는 switch가 항상 on이 되어 switching이 안될 수 있다. 잘 따져보고 써야한다.

'회로 공부' 카테고리의 다른 글

| OP-Amp (0) | 2024.11.11 |

|---|---|

| Switching 응용회로 / Comparator (1) | 2024.11.11 |

| MOSFET (0) | 2024.11.11 |

| Transistor - BJT 응용회로 (0) | 2024.11.11 |

| Diode 응용회로 (2) (0) | 2024.11.11 |