OP-Amp

- 아날로그 IC의 성능의 70%이상은 op-amp에 의해 결정될만큼 중요

Ideal한 Op-Amp에 대해서 먼저 살펴봄

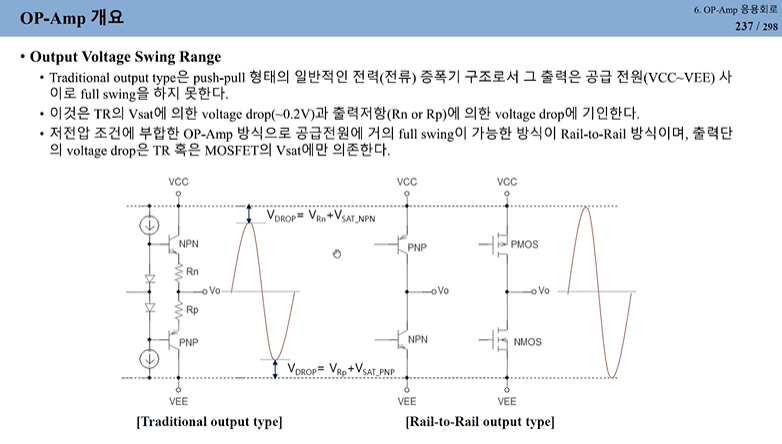

- 삼각형 형태의 symbol: 방향성을 가지고 있음. 왼쪽 → 오른쪽. 신호가 움직이는 방향 신호가 입력되는 곳이 왼쪽. 신호가 출력되는 곳이 오른쪽.

- 입력 2군데 한쪽을 - 한쪽을 +. - 입력단자 : 반전 입력단자 inverting input, + 입력단자 : 비반전 입력단자 non-inverting input.

- 차동입력. 요즘은 차동출력의 경우도 있다.

- DC 전원부분이 +전압과 - 전압에 연결되어있다. 대칭되는 전압값.

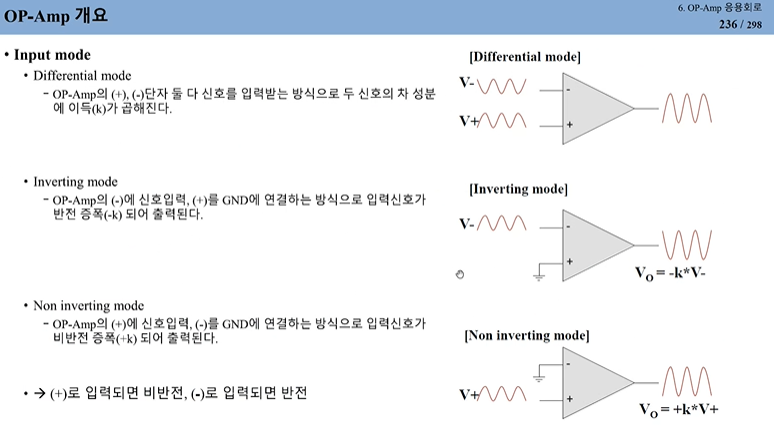

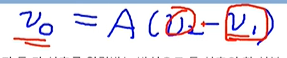

- V2 전압과 v1전압을 입력받아서 그 차이만큼 증폭되어 출력으로 나간다.

- 전압을 입력받아서 증폭한 뒤 전압을 출력하는 전압증폭기.

- 두 전압의 차이를 증폭시키는 차동증폭기.

Ideal한 전압증폭기

- A 라는 증폭도가 클수록 좋다 → 무한대로 간다.

- 전압을 입력받는 입력단의 입력저항이 커야한다. 그래야 입력을 잘 받는다. 입력저항이 무한대로 간다.

- 뒷단의 출력저항은 작을수록 좋음. 출력저항이 0으로 간다.

- A_cm이 0으로 간다.

- 주파수에 관계없이 일정한 이득 → 대역폭 BW가 무한대로 간다.

Ideal한 차동증폭기

- 두 신호의 공통성분은 평균값으로 구한다. v1+v2/2. A_d = differential

- 차이성분만 증폭시켜야하는데 공통성분도 증폭시킨다. A_cm = common mode

- V_o = A_d(V_2-V_1)+A_cm((V_1+V_2)/2)

- A_cm 값이 0으로 가야한다.

- 차동신호를 증폭하는 증폭도는 크게 증가할수록 좋음. 공통신호를 증폭하는 증폭도는 작게 증가할수록 좋음. 두 값의 비 A_d/A_cm 이 클수록 좋음. CMRR = common mode rejection rate. 값이 커서 로그를 취해 dB값으로 계산.

- 첫번째 조건 잘 만족.

- BJT로 만들어진 op-amp는 수 MegOhm. FET로 만들어지는 op-amp는 gate단자가 무한대 저항이기 때문에 실제 입력저항이 무한대. 두번째 조건 만족

- 출력저항은 50ohm 에서 수백 ohm을 가지고있음. Negative feedback이라는 구조를 만드는 순간 op-amp출력저항은 mOhm 단위로 떨어진다. 3,4 조건 잘 만족.

- Ideal한 op-amp거의 다 만족하는데 대역폭이 결정적인 단점. 실제로 사용하는 op-amp의 대역폭 수십 Hz밖에 안됨. 구간이 너무 작음. 그래서 op-amp는 negative feedback이라는 형태로 써야 증폭기로 쓸 수 있다.

- 증폭기를 트랜지스터로 만들면 그 과정이 복잡함. 예를 들어 npn을 사용하면 collector emitter base에 전압들을 고정시켜서 bias를 잡아야됨 → 쉽지 않음

- 동작점에 따라 달라지는 소신호 parameter들을 뽑아야됨.

- Op-amp를 사용하면 supply 만 연결해주면 bias가 알아서 잡힌다.

- 첫번째 네번째 장점 굉장히 좋음 → 더이상 transistor를 증폭기로 사용하지 않는다.

- 차동증폭기: 하나의 입력에 두개의 트랜지스터

차동증폭기의 장점: noise에 강하다

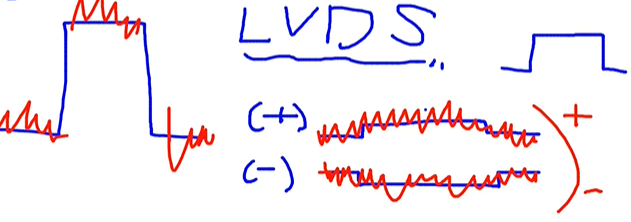

- 차동구조는 두 입력으로 들어오는 신호를 빼기해서 그 신호를 증폭시킨다. 크기는 같은데 위상이 180도 다른 신호 : 완전 차동신호.

- 두 신호에 똑같은 noise가 들어오고 두 입력의 차이를 증폭하면 신호의 진폭이 두배가 되고 noise는 상쇄된다.

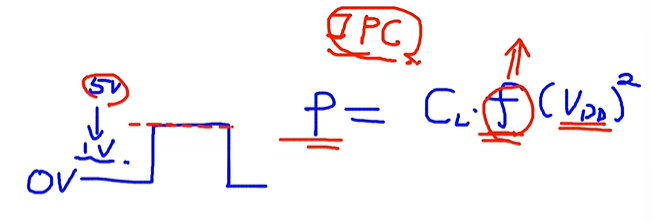

디지털 신호를 보내는 ic의 power 소모

- 성능을 끌어올리기 위해서 동작 주파수를 높임. 요즘 cpu는 GHz 단위.

- 한 클럭당 수행할 수 있는 명령: IPC

- 클럭을 늘리니까 power 소모도 커져 열이남. 동작 전압을 떨어뜨리면 power소모가 줄어듦.

- 성능을 늘리기 위해 동작 전압을 떨어뜨려서 디지털신호인데도 논리 0과 논리 1을 구분하기 힘들어짐.

- 디지털에서도 차동증폭을 사용해서 신호를 증폭시키고 noise를 줄인다. → Low Voltage Differential Signal (LVDS)

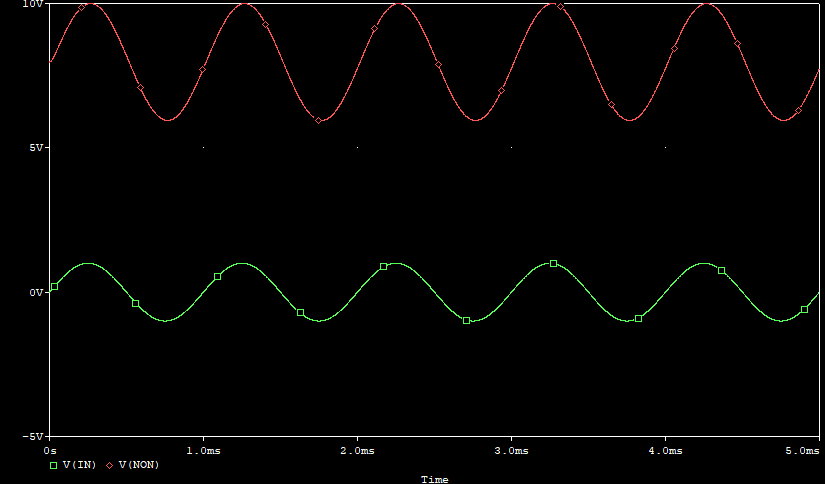

V_2가 비반전, V_1이 반전

- 비반전모드 → 출력이 입력된 신호와 같은 위상

- 반전모드 → 출력이 입력된 신호와 180도 뒤집어진 위상이 됨

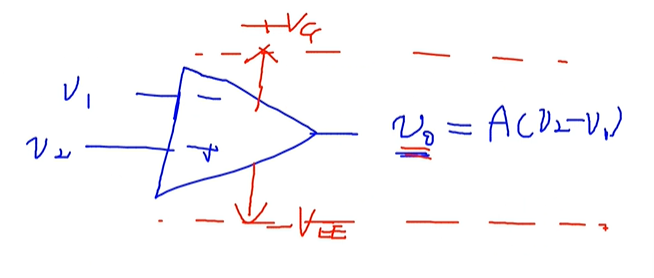

- Op-amp의 출력은 어디까지 나올 수 있을까?

- 내가 걸어준 supply 전압까지 (에너지 보존법칙)

- 일반적으로 0.몇에서 1V 정도 빠진 만큼이 최대 나올 수 있는 전압. 요즘처럼 저전압으로 동작시키는 op-amp는 거의 supply 전압에 가까운 출력전압이 나온다.

출력전압을 0으로 만드는 방법 (비정상적인 출력전압)

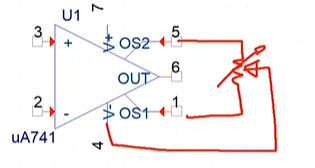

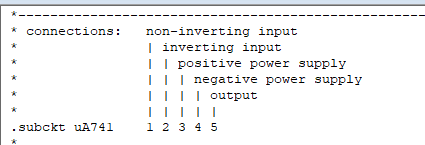

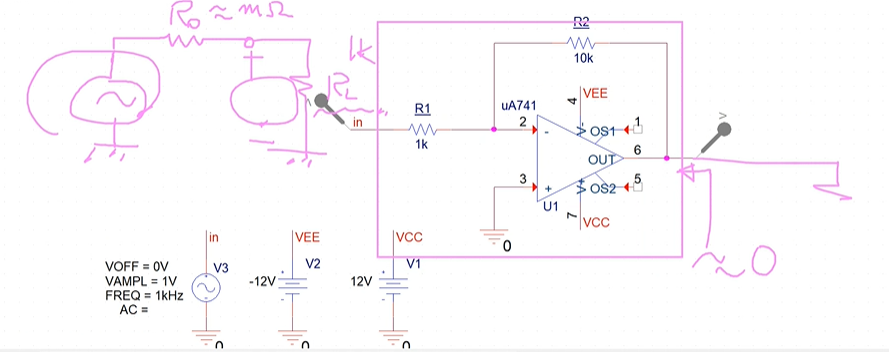

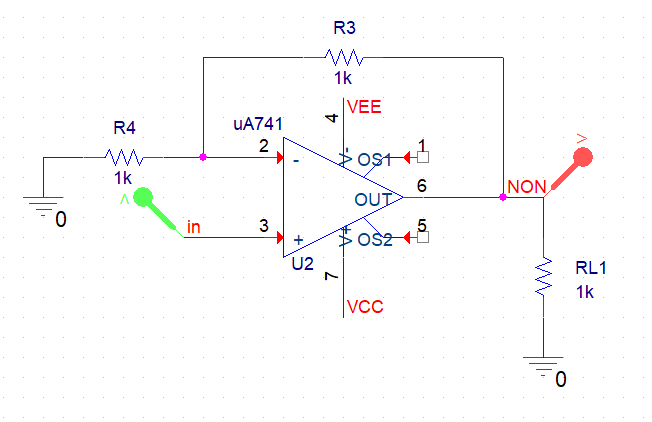

- Pspice 모델의경우 1번핀과 5번핀에 세팅이 안되어있다.

- 비반전, 반전, +supply, -supply, 출력

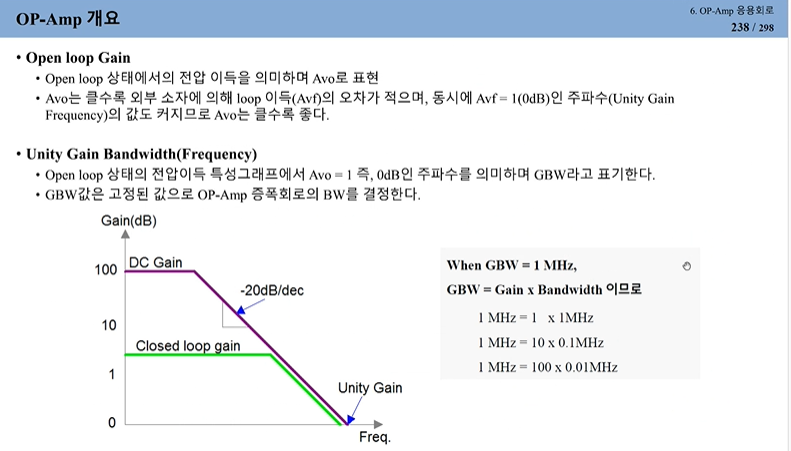

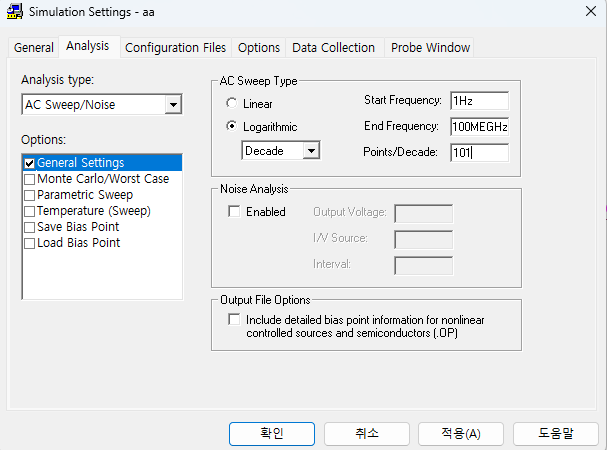

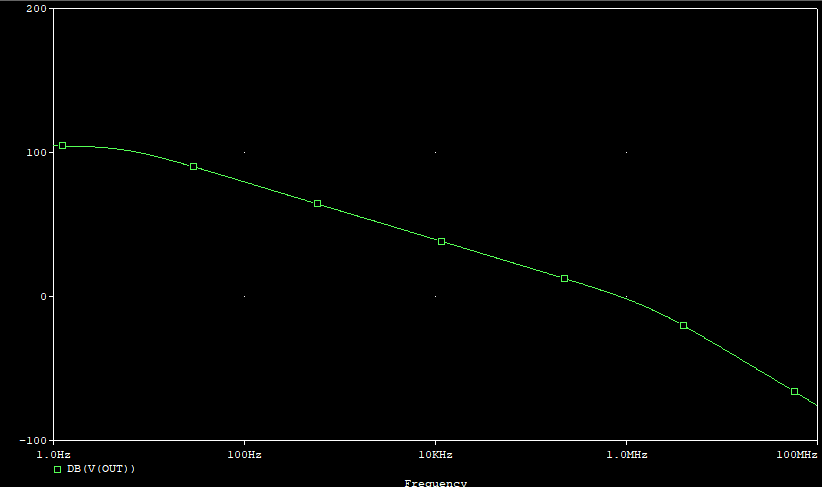

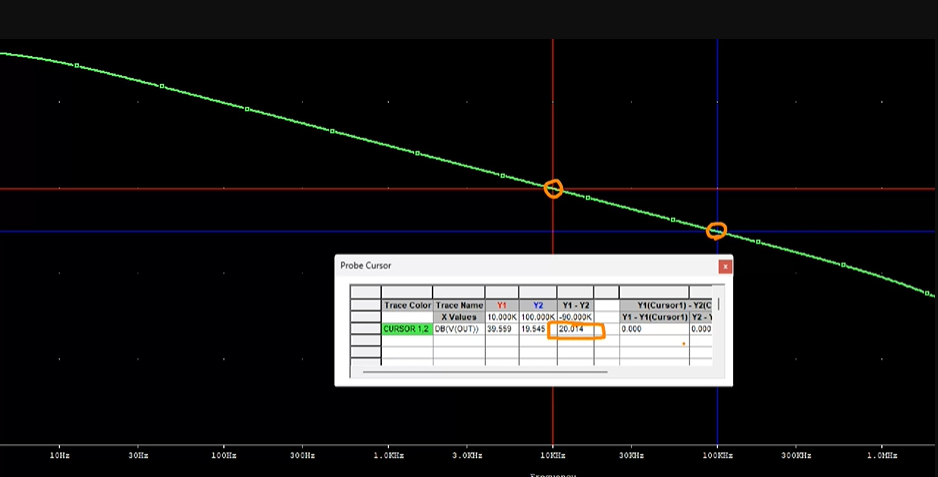

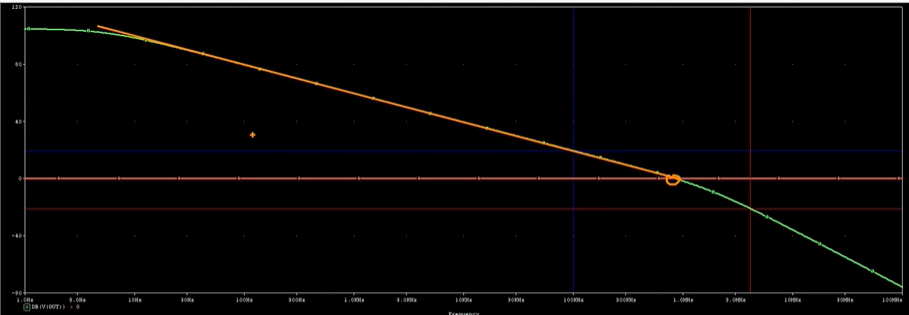

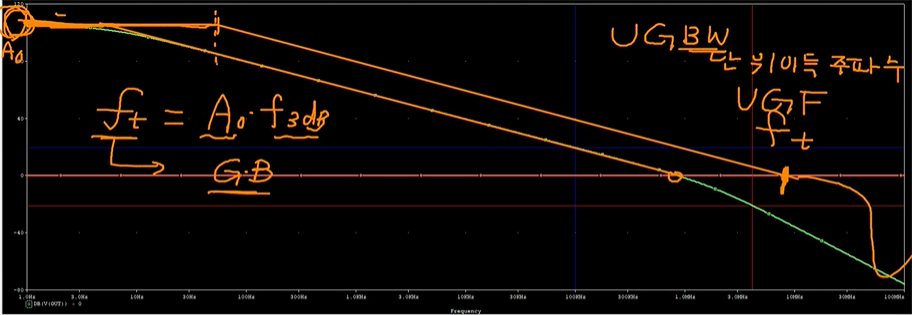

- 주파수가 10배차이 날때 -20dB차이

- 기울기가 일정하다. 낮은쪽에 극점이 하나 있는 Low Pass Filter와 비슷함.

- 0dB을 지나고 나서는 상관 없음.

- 시작하는 위치와 대역폭만 다르다.

- 단위 이득 주파수 (Unity Gain Frequency / Bandwidth) (UGF/UGB) f_t

- 이득이 1이되는 주파수가 중요한 이유

- UGB가 클수록 고속으로 동작하는 신호를 다룰 수 있다.

- 3dB떨어지는 cut-off frequency에 직류 이득을 곱하면 단위 이득 주파수가 됨

- Gain Bandwidth product

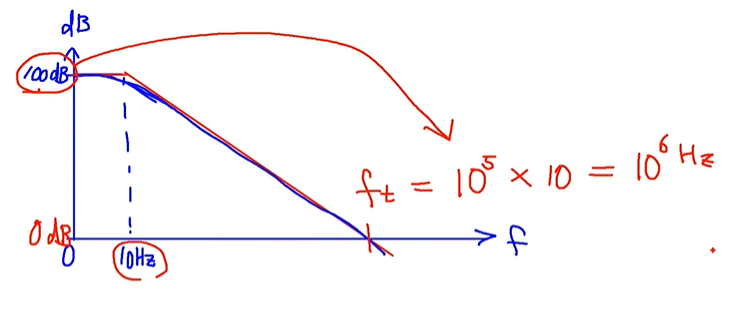

단위이득주파수는?

- 100dB = 10^5

- F_t = 이득*Bandwidth = 10^5*10 = 10^6 Hz

- 대역폭이 10Hz밖에 안되서 op-amp자체로만 증폭기로 사용할 수 없다.

- 주변에 어떤 회로를 붙혀서 Negative Feedback을 만들어줘서 대역폭을 늘려야함.

Negative Feedback이란?

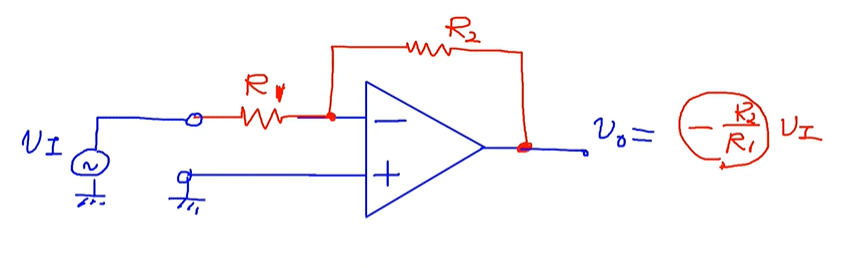

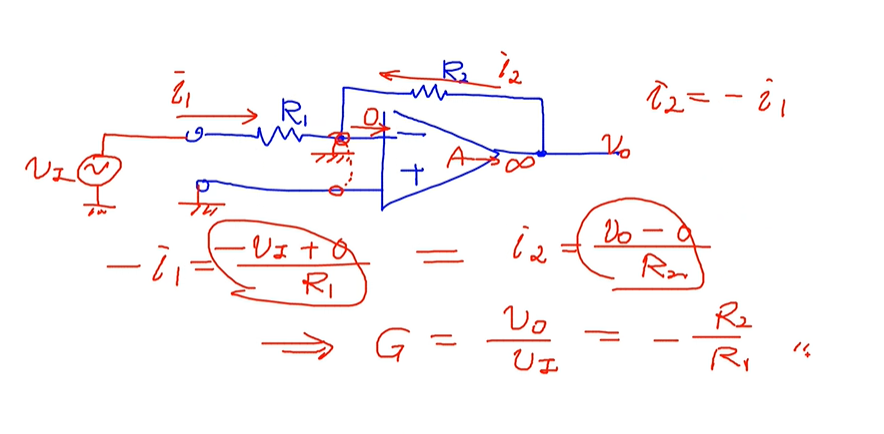

반전 증폭기

- Feedback: 제어할 때 필요

- 출력이 어떤식으로 나오는지를 보고 입력과 비교를 할때 빼기를 해서 차이가 작아지는 방향으로 제어를 하는것.

- 출력으로 나오는 신호를 계속 입력으로 넣으면 계속 더 커짐 아니면 계속 작아짐. (positive feedback). 아날로그 신호 증폭용도로는 절대 안됨.

- 출력을 - 단자 쪽으로 넣어주는것이 negative feedback.

- 반전 증폭기의 증폭도 : -R2/R1

- 10배 증폭시키고 싶으면 R2:R1을 10:1로 쓰면 된다. 다른 고려사항 없음.

- 저항의 비에 의해서만 증폭도가 결정되는것의 장점: 정밀저항 (오차 3%이내)을 사용하면 이득이 정밀하게 세팅된다.

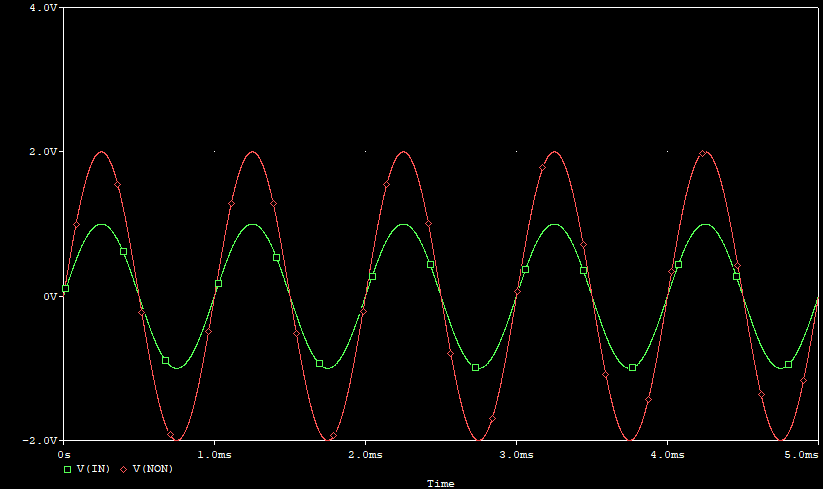

- -의 의미: 입력신호와 출력신호의 위상이 180도 뒤집어져있다.

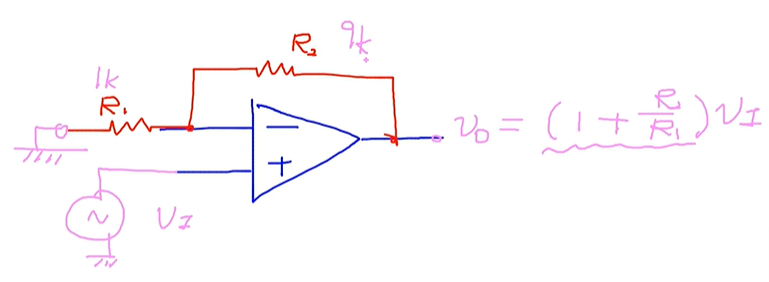

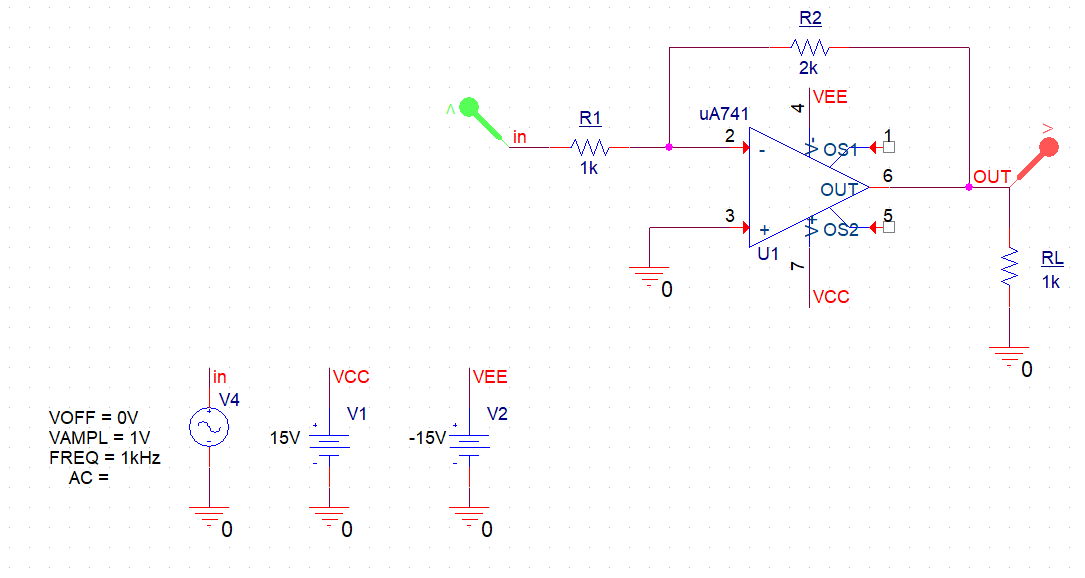

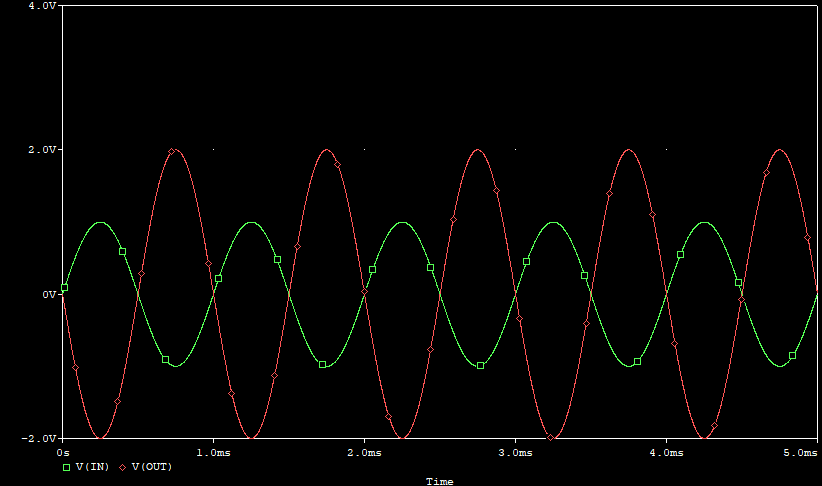

비반전 증폭기

- 전압이득을 원하는대로 세팅하기 쉬움

- 10배 증폭을 원하면 R2를 9k, R1을 1k로 사용하면 됨

- 현업에서 위 두 증폭기가 가장 많이 쓰임

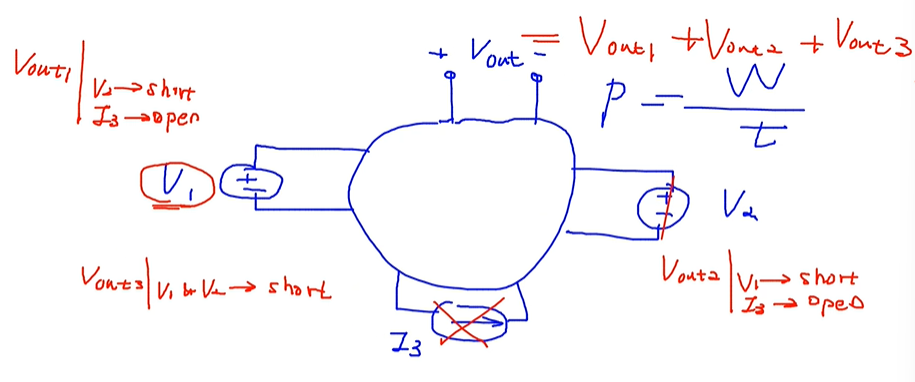

중첩의 원리 (superposition)

- 어떤 회로를 구동시키기 위해 필요한것 전원 V_1

- 출력 V_out은 전원에 의해서만 결정

- Power = W(에너지)/t(시간)

- 전원이 하나이면 옴의법칙, 키르히호프를 사용하면 해결할 수 있음

- 전압원이 2개이면 V_1, V_2 둘다 회로에 기여. 전류원 I_3도 회로에 기여

- 어떻게 기여? 각개격파

- V1 전압원의 기여만 보기위해 V2, I3를 없다고 취급. 전압원 V2를 short시킴. 전류원 I3를 open 시킴.

- V2 전압원의 기여만 보기위해 V1, I3를 없다고 취급. 전압원 V1을 short시킴. 전류원 I3를 open 시킴.

- I3 전류원의 기여만 보기위해 V1, V2를 없다고 취급. 전압원 V1, V2를 short시킴.

- 최종 V_out = V_out1+V_out2+V_out3

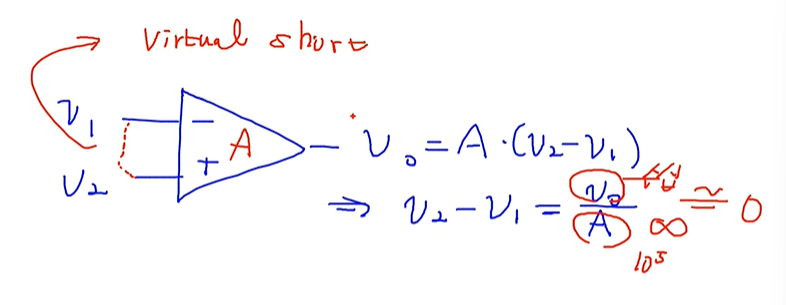

- Op-amp의 증폭도가 크다라고 가정을 하면 V1 V2를 거의 같은 전압으로 본다. 해석할때는 V1, V2를 short시킨것과 같다. 가상단락 (virtual short) 을 적용하면 op-amp 회로 해석이 쉬워짐.

- 실제로 사용하는 op-amp에서도 A가 충분히 크다.

반전 증폭기의 증폭도

- 가상접지 (virtual ground)

- I_1 = (V_i-0)/R_1, I_2 = (V_o-0)/R_2

- Ideal한 op-amp라고 가정을 하면 입력저항이 무한대. Op-amp의 입력단으로 전류가 못흐른다. i_1 , I_2는 크기가 같고 방향이 반대인 전류.

- 전압 이득 G = V_o/V_I = -R2/R1

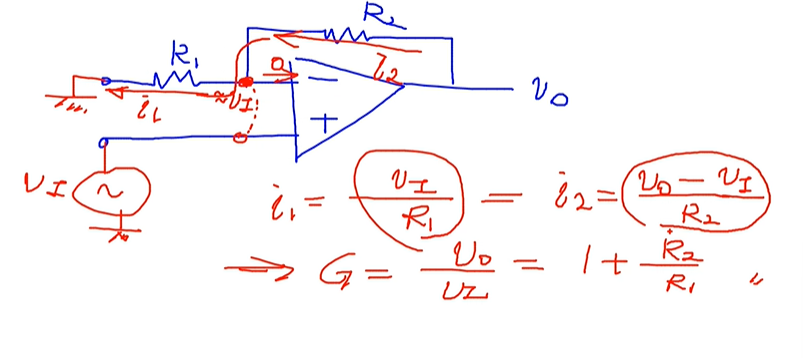

비반전 증폭기의 증폭도

- Virtual short에 의해 -,+ 단자 사이의 전압이 V_i가 된다.

- I_1 = V_I/R1, I2 = (V_o-V_I)/R2

- I_1 = i_2

- 전압 이득 G = V_o/V_I = 1+ R2/R1

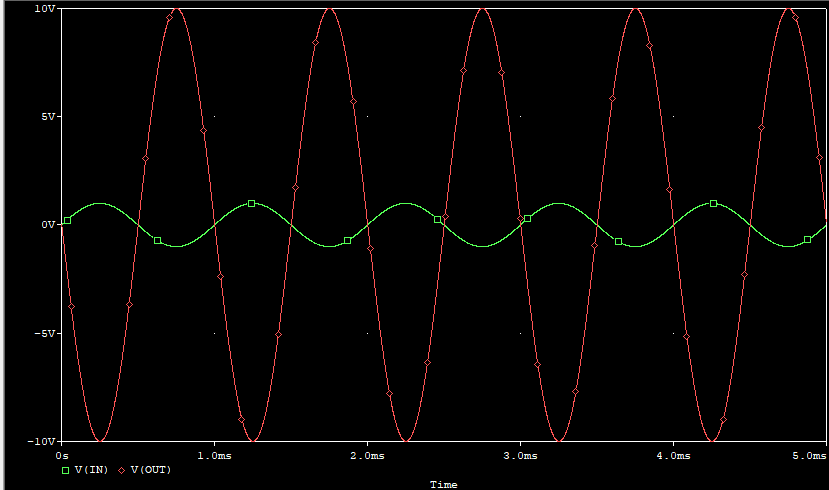

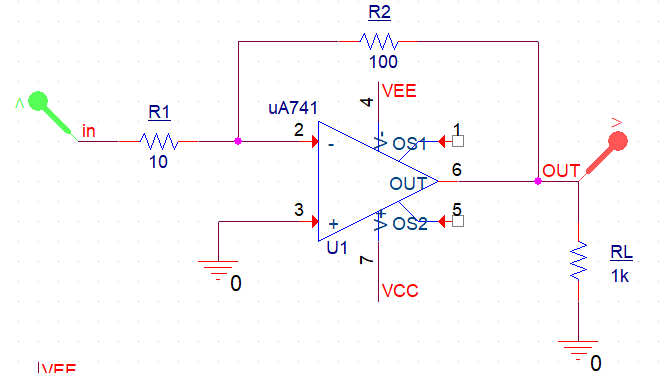

이득이 -2인 반전 증폭기

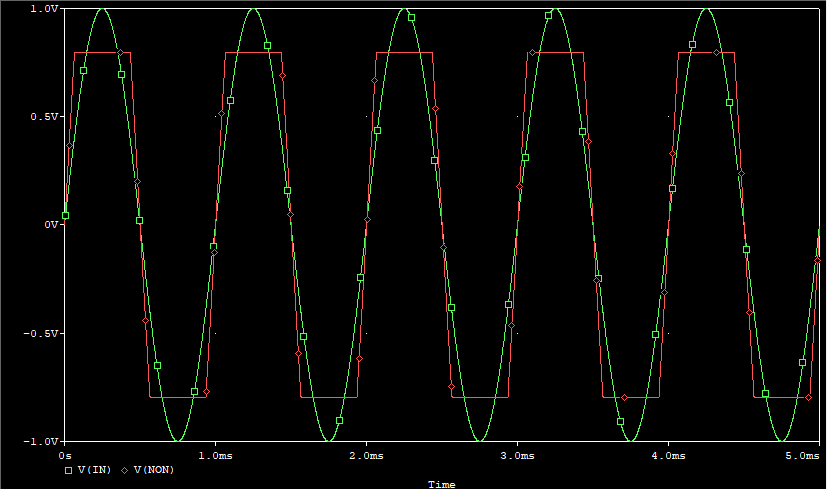

R2를 10으로 바꾸면

R2를 15k로 바꾸면

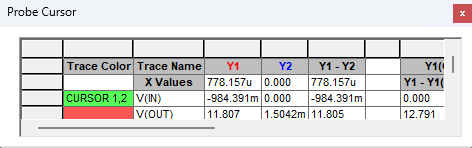

- 최대(정격) 출력전압 Vo_max: 11.8V 정도

부하 R_L은 op-amp 출력에 영향이 없다. 왜?

- Ideal op-amp의 특성 : negative feedback을 걸면 op-amp출력저항은 거의 0이다.

- Op-amp 전체의 출력단: 굉장히 작은 저항. 뒷단으로 출력 (증폭된 전압 결과)이 잘 전달된다.

- Op-amp가 달려있는 능동필터가 값을 잘 넘겨준다.

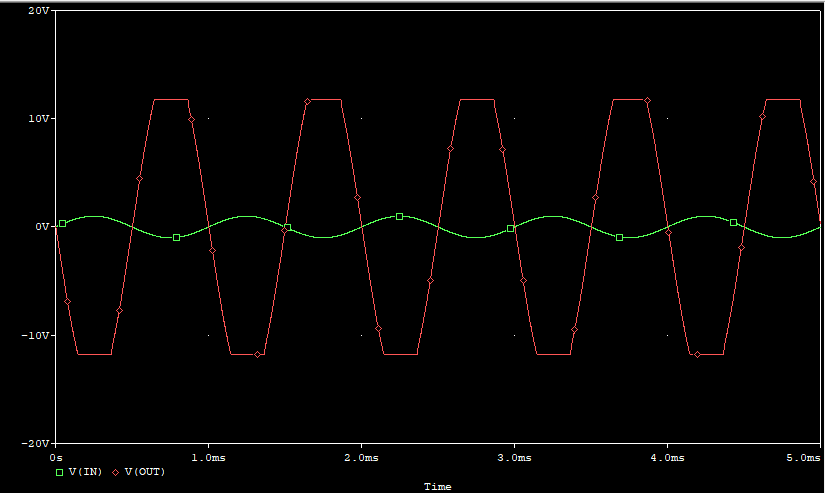

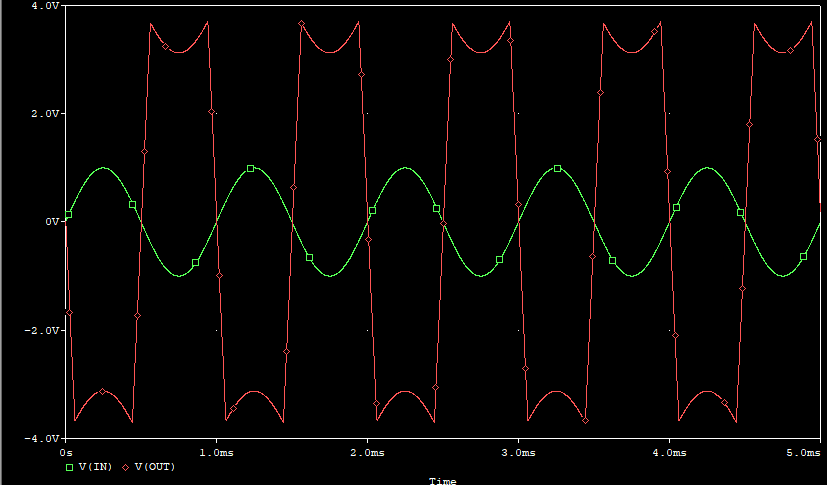

신호가 왜곡되는 경우 R1 = 10, R2 = 100이면 10배 증폭이 되어야하는데 결과가 이상하게 나옴.

- 전압이 나올때는 전압만 나오는것이 아닌 전류도 나온다.

- 일반적인 op-amp에서는 수십 mA정도 가 op-Amp의 출력전류의 최대값 이다.

- Maximum +/- 40mA

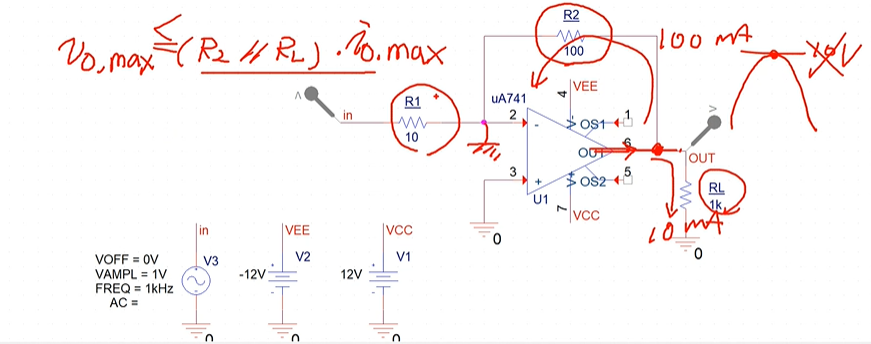

- 정상적으로 10V까지 올라갈수 있다면 op-amp의 출력단에서 전류가 얼마나 흐를 수 있는지 고려

- Virtual Short에 의해 10V/100ohm = 100mA 10V/1kohm= 10mA → 110 mA가 흘러야되는데 내어줄수 있는 최대 전류까지만 흐른다.

- R2와 R1이 병렬 연결될 수 있는 최대전류 io_max

- Op-amp에서 내어줄 수 있는 최대출력(정격) 전류가 출력 전압에 영향을 줄 수 있음. R_L 값이 이때는 영향을 줄 수 있다.

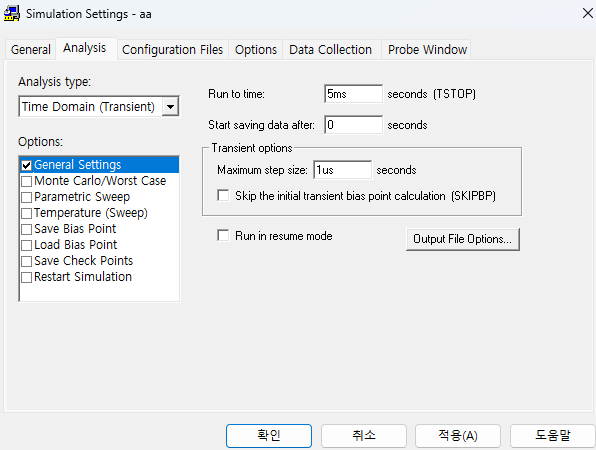

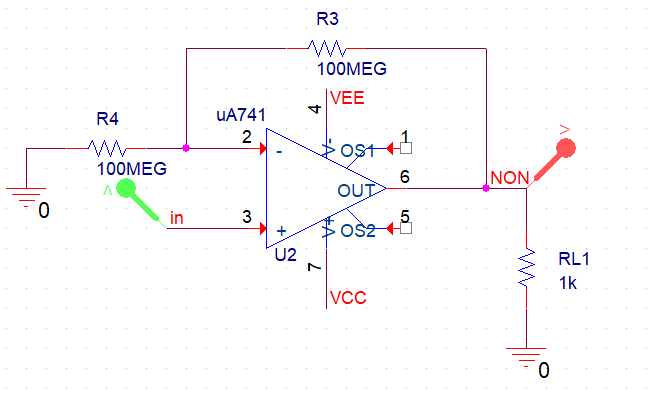

이득이 +2가되는 비반전 증폭기

10 ohm 10 ohm으로 바꿨을때

- 10k 와 10ohm이 병렬 연결 → 작은 저항을 쓰면 큰 전류가 흐르는 상황이 되어서 op-amp의 값이 정상적이지 않을 수 있다.

- 1megohm 까지는 정상적인데 10megohm 부터 출력 전압이 이상해짐.

- Op-amp를 쓸때 Kohm 단위를 쓰면 적당하다.

'회로 공부' 카테고리의 다른 글

| OP-Amp(3) (0) | 2024.11.11 |

|---|---|

| OP-Amp(2) (0) | 2024.11.11 |

| Switching 응용회로 / Comparator (1) | 2024.11.11 |

| MOSFET Load Switching 회로 (0) | 2024.11.11 |

| MOSFET (0) | 2024.11.11 |